RM0444 Rev 5 333/1390

RM0444 Extended interrupt and event controller (EXTI)

335

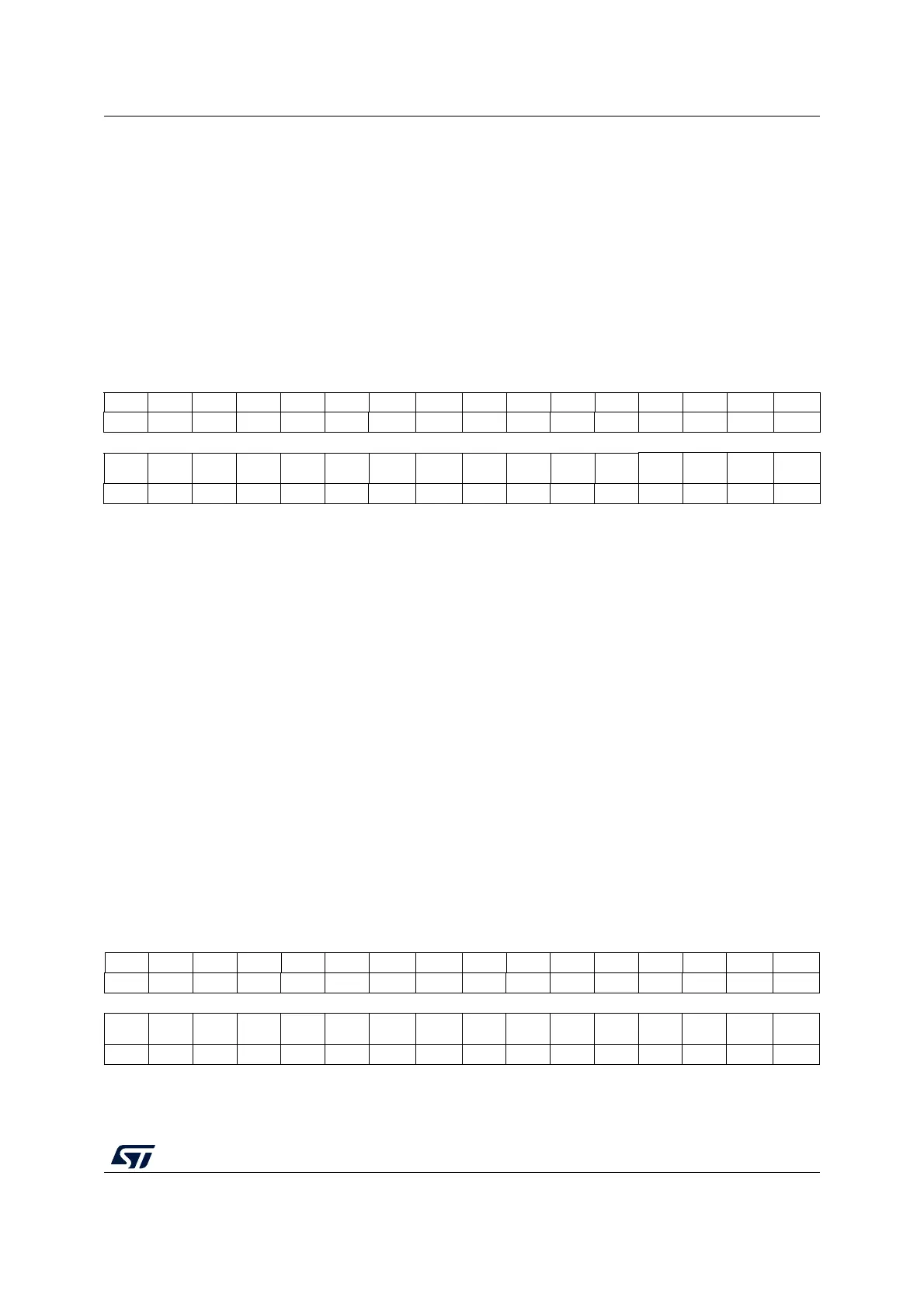

13.5.14 EXTI CPU wakeup with interrupt mask register (EXTI_IMR2)

Address offset: 0x090 (EXTI_IMR2)

Reset value: 0xFFFF FFFF

Contains register bits for configurable events and direct events.

The reset value is set such as to, by default, enable interrupt from direct lines, and disable

interrupt from configurable lines.

This register is not available in

STM32G031xx and STM32G041xx as well as STM32G051xx and

STM32G061xx

.

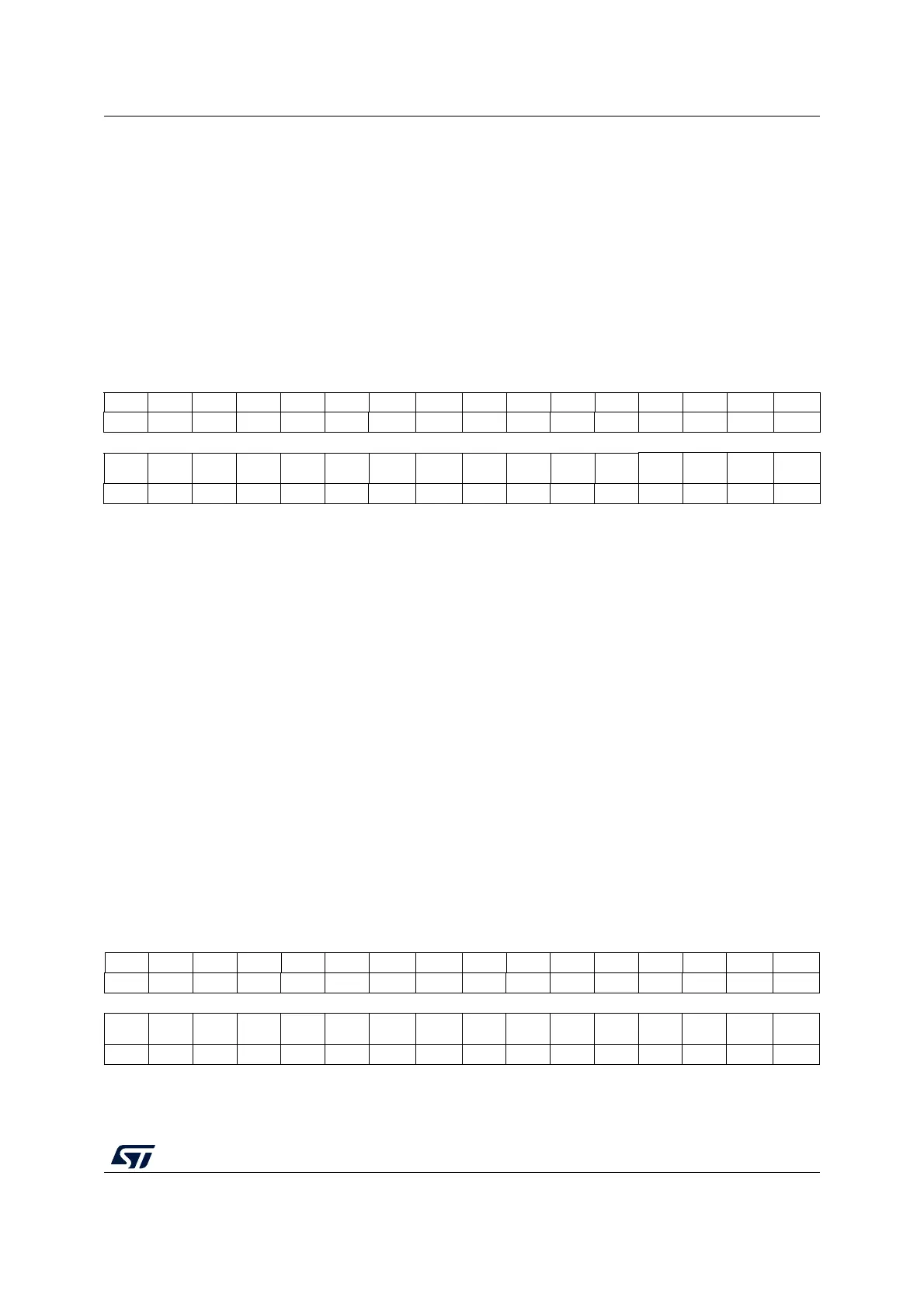

13.5.15 EXTI CPU wakeup with event mask register (EXTI_EMR2)

Address offset: 0x094

Reset value: 0x0000 0000

Contains register bits for configurable events and direct events.

The reset value is set such as to, by default, enable interrupt from direct lines, and disable

interrupt from configurable lines.

This register is not available in

STM32G031xx and STM32G041xx as well as STM32G051xx and

STM32G061xx

.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 7654321 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. IM35 IM34 IM33 IM32

rw rw rw rw

Bits 31:4 Reserved, must be kept at reset value.

Bits 3:0 IMx: CPU wakeup with interrupt mask on line x (x = 35 to 32)

Setting/clearing this bit unmasks/masks the CPU wakeup with interrupt, by an event on the

corresponding line.

0: wakeup with interrupt request from Line x is masked

1: wakeup with interrupt request from Line x is unmasked

The IM35 and IM34 bits are only available in STM32G0B1xx and STM32G0C1xx. They

are reserved in STM32G071xx and STM32G081xx.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. EM35 EM34 EM33 EM32

rw rw rw rw

Loading...

Loading...