Embedded Flash memory (FLASH) RM0444

92/1390 RM0444 Rev 5

The System memory area is read-accessible whatever the protection level. It is never

accessible for program/erase operation.

Level 0: no protection

Read, program and erase operations within the Main Flash memory area are possible. The

option bytes and the backup registers are also accessible by all operations.

Level 1: Read protection

Level 1 read protection is set when the RDP byte and the RDP complemented byte contain

any value combinations other than [0xAA, 0x55] and [0xCC, 0x33]. Level 1 is the default

protection level when RDP option byte is erased.

• User mode: Code executing in user mode (boot from user Flash memory) can access

Main Flash memory, option bytes and backup registers with all operations.

• Debug, boot from SRAM, and boot from System memory modes: In debug mode

or when code boots from SRAM or System memory, the Main Flash memory and the

backup registers (TAMP_BKPxR in TAMP) are totally inaccessible. In these modes, a

read or write access to the Flash memory generates a bus error and a Hard Fault

interrupt.

Caution: In Level 1 with no PCROP areas defined, it is mandatory to set PCROP_RDP bit to 1 (full

mass erase when the RDP level is decreased from Level 1 to Level 0). In Level 1 with a

PCROP area defined, user code to protect by RDP but not by PCROP must be placed

outside pages containing a PCROP-protected subpage.

Level 2: No debug

In this level, the protection Level 1 is guaranteed. In addition, the CPU debug port, the boot

from RAM (boot RAM mode) and the boot from System memory (boot loader mode) are no

more available. In user execution mode (boot FLASH mode), all operations are allowed on

the Main Flash memory.

Note: The CPU debug port is also disabled under reset.

Note: STMicroelectronics is not able to perform analysis on defective parts on which the Level 2

protection has been set.

Changing the read protection level

The read protection level can change:

• from Level 0 to Level 1, upon changing the value of the RDP byte to any value except

0xCC

• from Level 0 or Level 1 to Level 2, upon changing the value of the RDP byte to 0xCC

• from Level 1 to Level 0, upon changing the value of the RDP byte to 0xAA

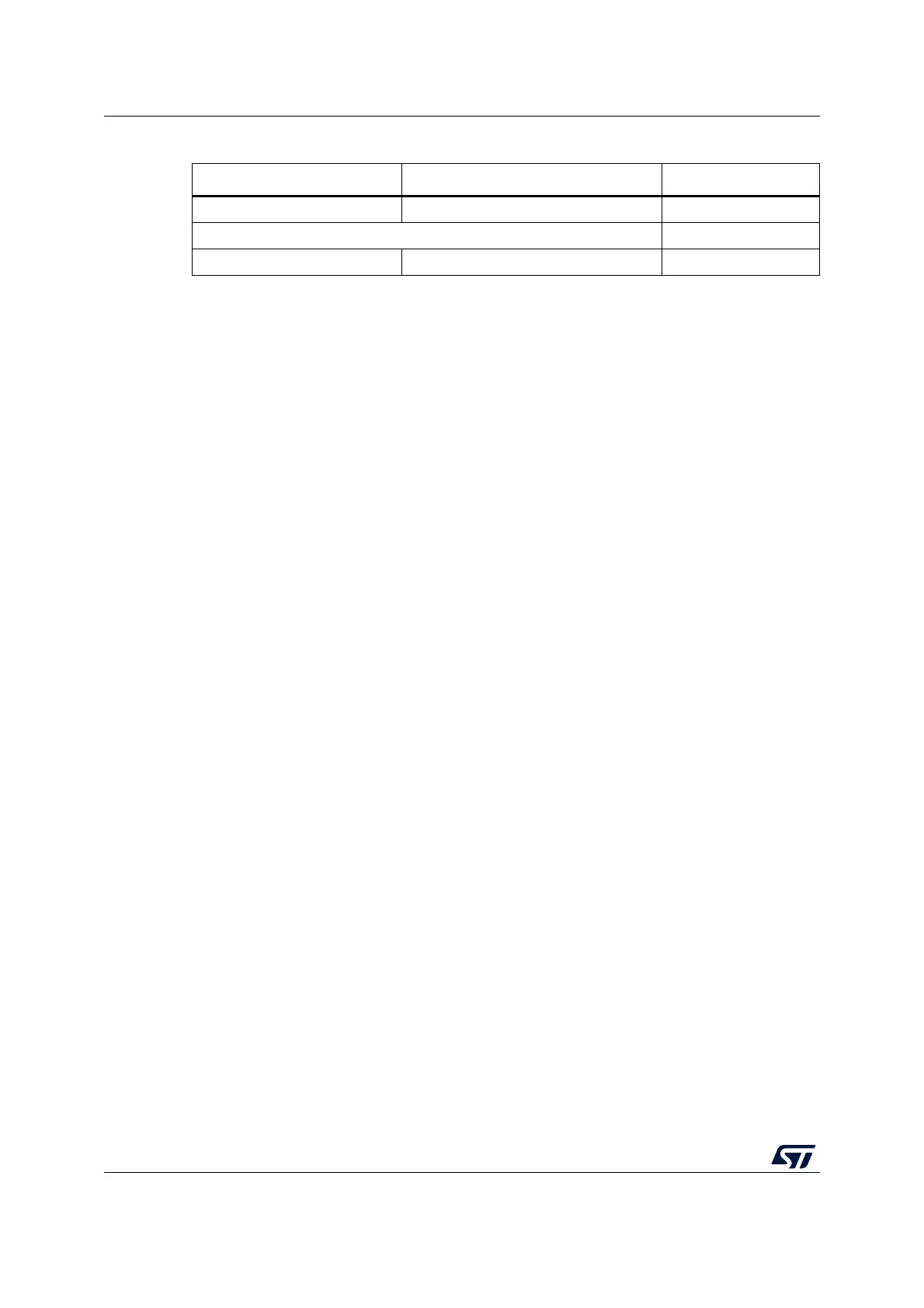

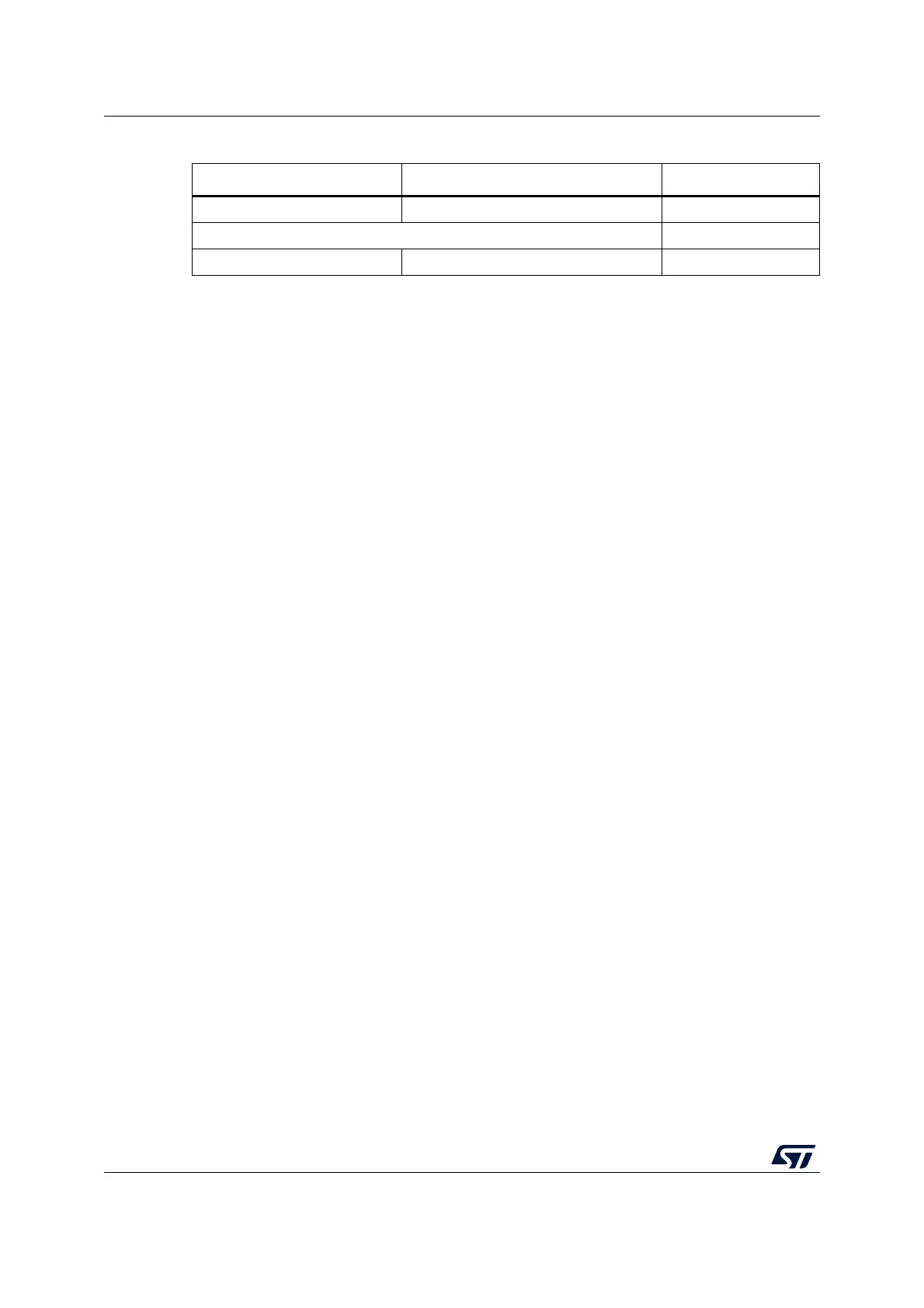

Table 17. Flash memory read protection status

RDP byte value RDP complement byte value Read protection level

0xAA 0x55 Level 0

Any values except the combinations [0xAA, 0x55] and [0xCC, 0x33] Level 1 (default)

0xCC 0x33 Level 2

Loading...

Loading...