RM0444 Rev 5 93/1390

RM0444 Embedded Flash memory (FLASH)

118

Once in Level 2, it is no more possible to modify the read protection level.

With the PCROP_RDP bit of the FLASH PCROP area A end address register

(FLASH_PCROP1AER) set, the change from Level 1 to Level 0 triggers full mass erase of

the Main Flash memory. The backup registers (TAMP_BKPxR) are also erased. The user

options except PCROP protection are set to their previous values copied from

FLASH_OPTR and FLASH_WRPyxR (x = A or B, y = 1 or 2). PCROP is disabled. The OTP

area is not affected by mass erase and remains unchanged.

With the PCROP_RDP bit cleared, a partial mass erase occurs, only erasing Flash memory

pages that do not overlap with PCROP area (do not contain any PCROP-protected

subpage). The option bytes are re-programmed with their previous values. This is also true

for FLASH_PCROP1xSR and FLASH_PCROP1xER registers (x = A or B).

Note: Mass erase (full or partial) is only triggered by the RDP regression from Level 1 to Level 0.

RDP level increase (Level 0 to Level 1, 1 to 2, or 0 to 2) does not cause any mass erase.

To validate the protection level change, the option bytes must be reloaded by setting the

OBL_LAUNCH bit of the FLASH control register (FLASH_CR).

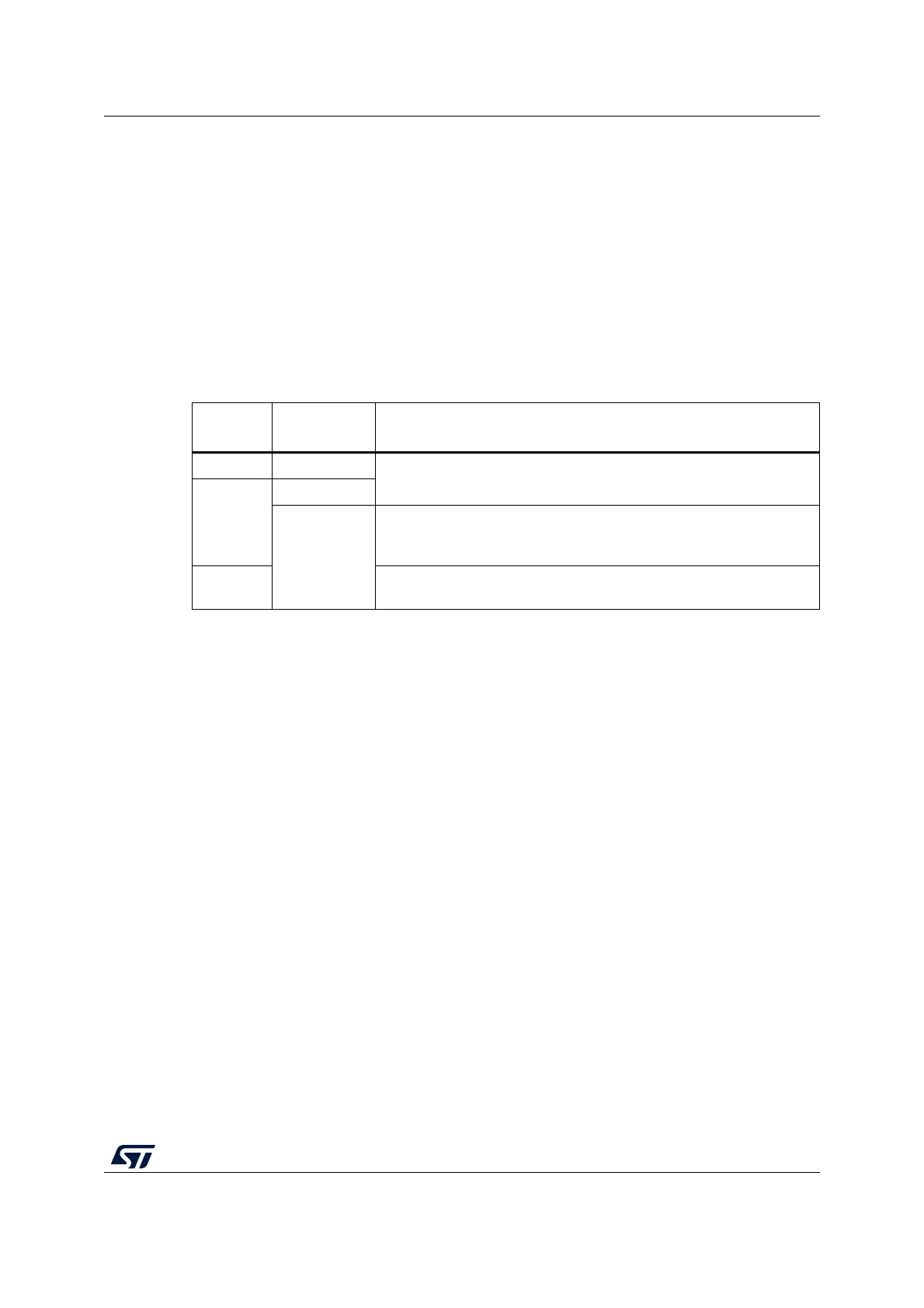

Table 18: Mass erase upon RDP regression from Level 1 to Level 0

PCROP

area

PCROP_RDP Mass erase

None x

Full

(Flash memory and backup register)

Part of

Flash

memory

1

0

Partial

(Flash memory pages not overlapping with PCROP area, and backup

registers)

Full Flash

memory

None

Loading...

Loading...