Reset and clock control (RCC) RM0444

212/1390 RM0444 Rev 5

5.4.22 Peripherals independent clock configuration register 2

(RCC_CCIPR2)

This register is only available on STM32G0B1xx and STM32G0C1xx. Reserved on the

other devices.

Address: 0x58

Reset value: 0x0000 0000

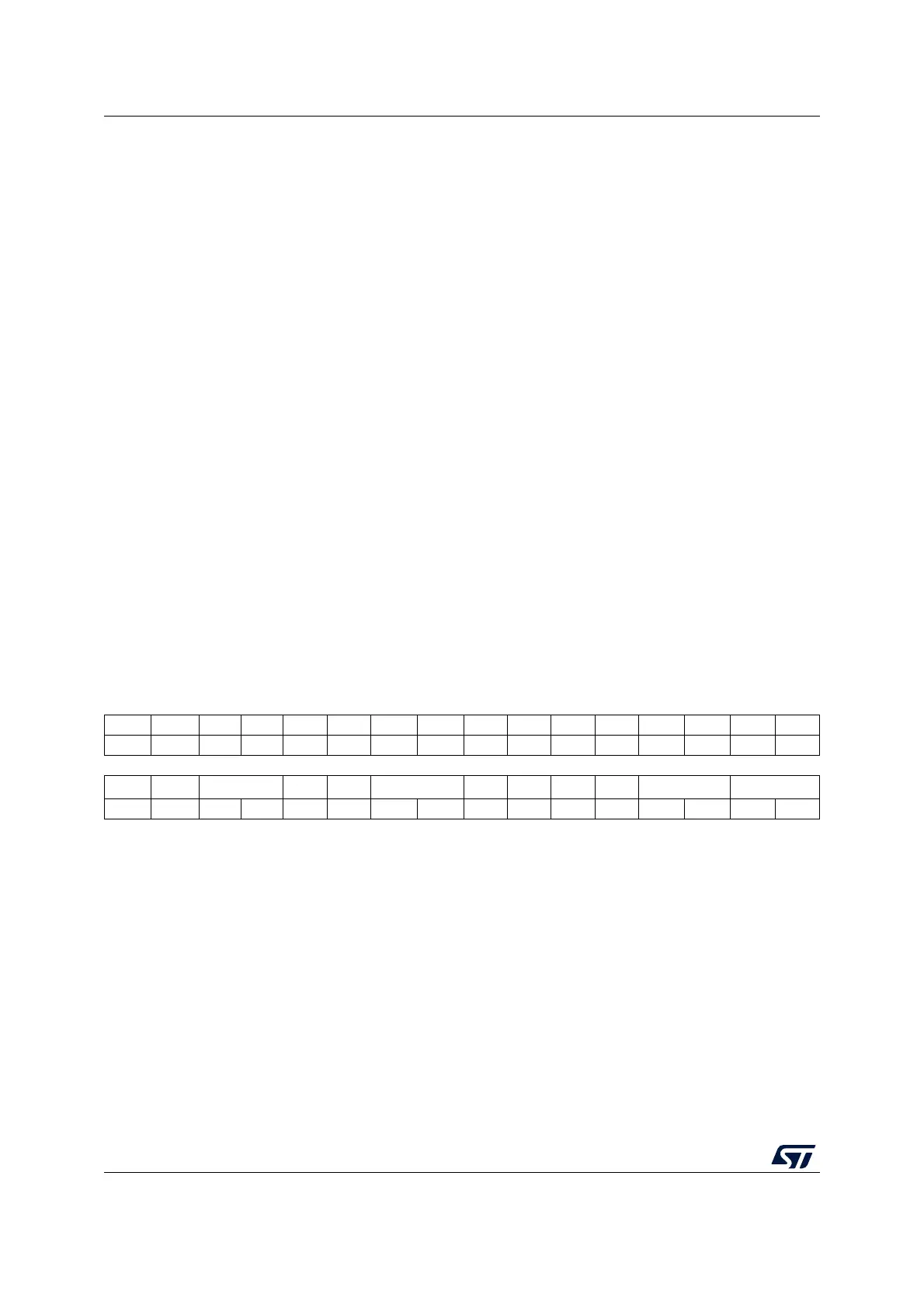

Bits 5:4 USART3SEL[1:0]: USART3 clock source selection

(1)

This bitfield is controlled by software to select USART2 clock source as follows:

00: PCLK

01: SYSCLK

10: HSI16

11: LSE

Bits 3:2 USART2SEL[1:0]: USART2 clock source selection

(1)

This bitfield is controlled by software to select USART2 clock source as follows:

00: PCLK

01: SYSCLK

10: HSI16

11: LSE

Bits 1:0 USART1SEL[1:0]: USART1 clock source selection

This bitfield is controlled by software to select USART1 clock source as follows:

00: PCLK

01: SYSCLK

10: HSI16

11: LSE

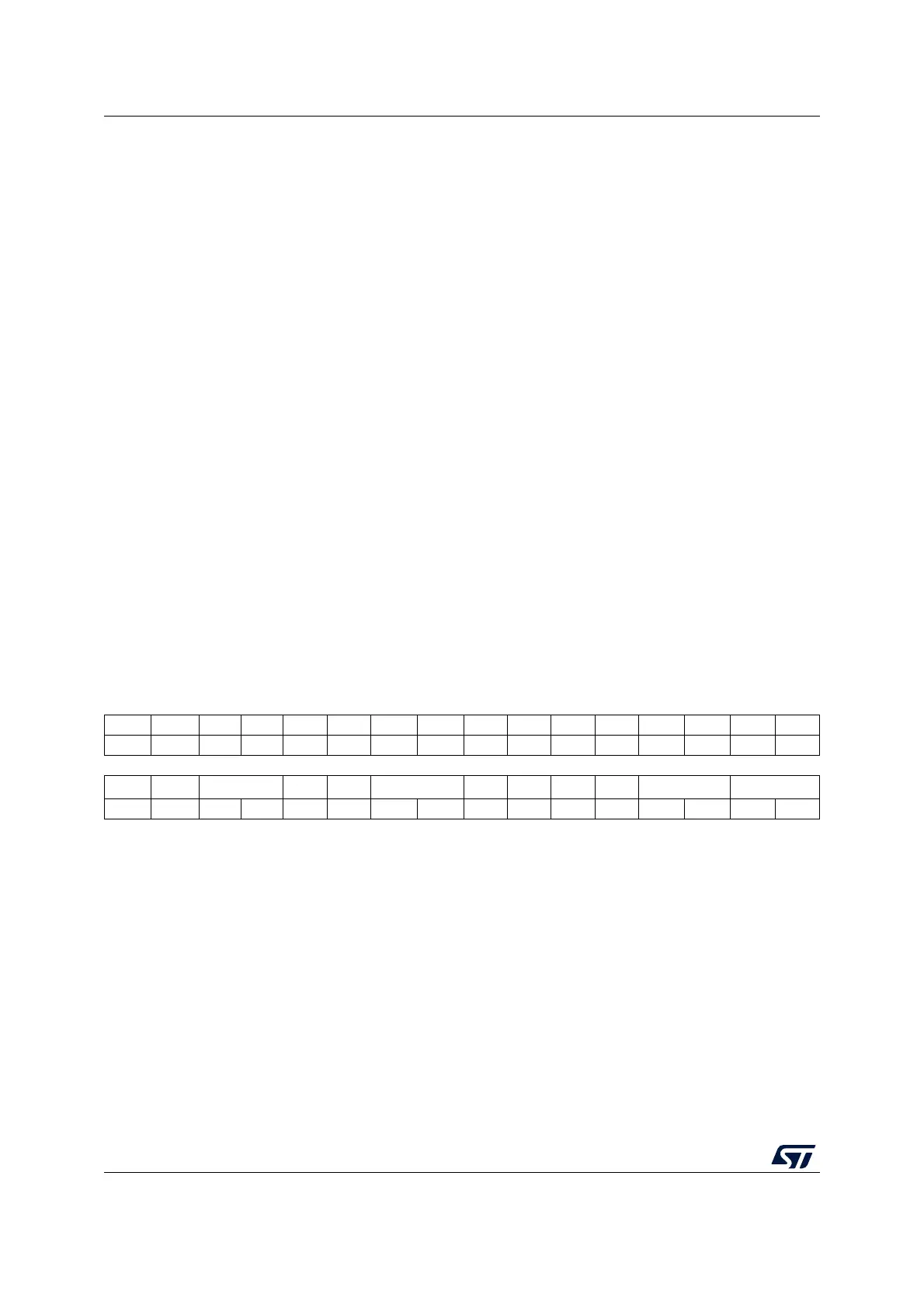

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res.

USBSEL

(1)

Res. Res. FDCANSEL Res. Res. Res. Res. I2S2SEL I2S1SEL

rw rw rw rw rw rw rw rw

1. Only significant on devices integrating the corresponding peripheral or function, otherwise reserved with zero reset value.

Refer to Section 1.4: Availability of peripherals.

Bits 31:14 Reserved, must be kept at reset value.

Bits 13:12 USBSEL[1:0]: USB clock source selection

This bitfield is controlled by software to select the USB clock as follows:

00: HSI48

01: PLLQCLK

(1)

10: HSE

11: Reserved

Bits 11:10 Reserved, must be kept at reset value.

Loading...

Loading...