Reset and clock control (RCC) RM0444

210/1390 RM0444 Rev 5

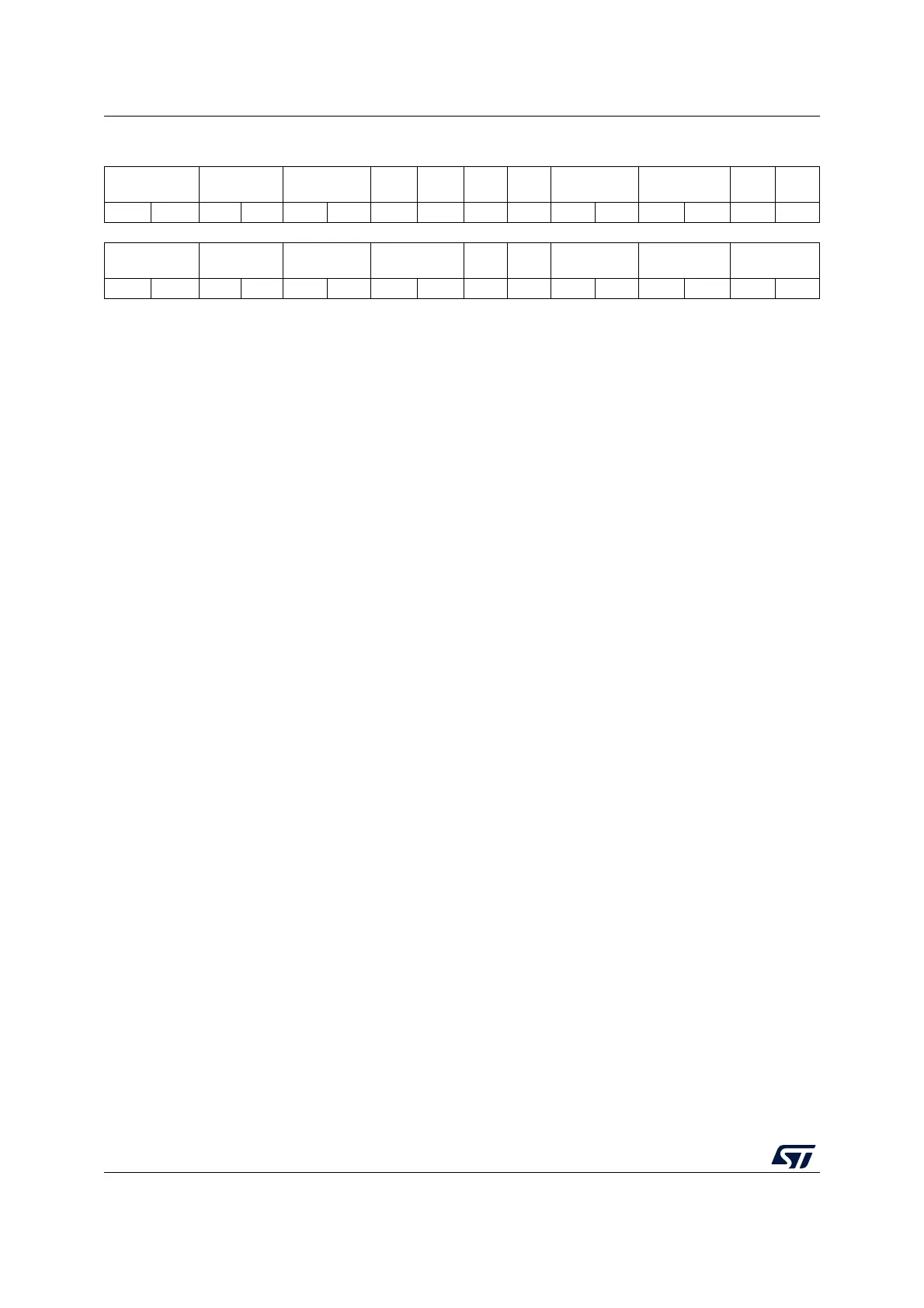

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

ADCSEL[1:0]

RNGDIV[1:0]

(1)

RNGSEL[1:0]

(1)

Res.

TIM15

SEL

(1)

Res.

TIM1

SEL

LPTIM2SEL[1:0] LPTIM1SEL[1:0] Res. Res.

rw rw rw rw rw rw rw rw rw rw rw rw

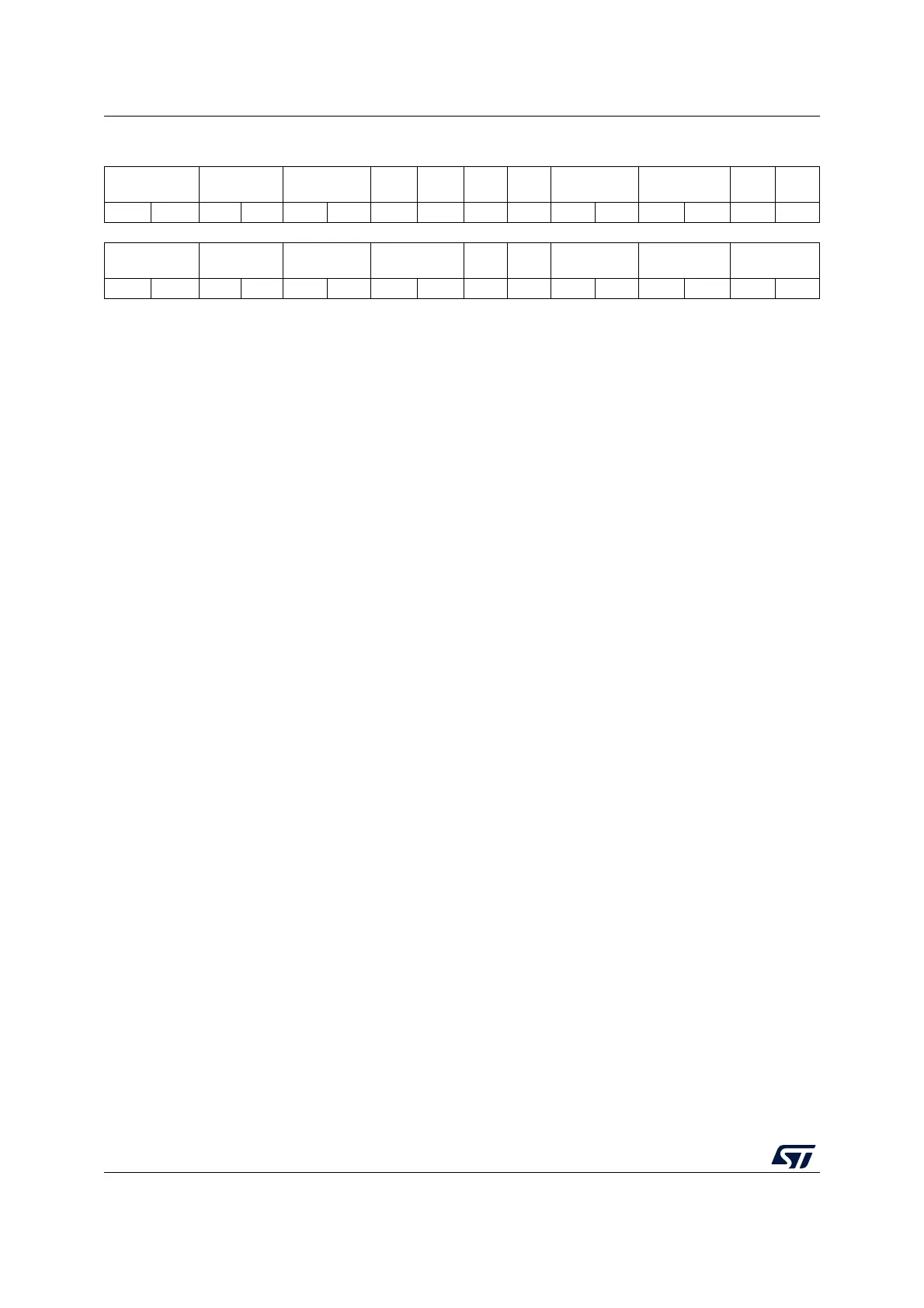

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

I2C2I2S1SEL[1:0] I2C1SEL[1:0]

LPUART1SEL

[1:0]

LPUART2SEL

[1:0]

(1)

Res.

CEC

SEL

USART3SEL

[1:0]

(1)

USART2SEL

[1:0]

(1)

USART1SEL

[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1. Only significant on devices integrating the corresponding peripheral supporting independent clock selection (or supporting

the corresponding function), otherwise reserved. Refer to Section 1.4: Availability of peripherals and Section 33.4: USART

implementation.

Bits 31:30 ADCSEL[1:0]: ADCs clock source selection

This bitfield is controlled by software to select the clock source for ADC:

00: System clock

01: PLLPCLK

10: HSI16

11: Reserved

Bits 29:28 RNGDIV[1:0]: Division factor of RNG clock divider

This bitfield is controlled by software to select the division factor as follows:

00: 1

01: 2

10: 4

11: 8

Bits 27:26 RNGSEL[1:0]: RNG clock source selection

This bitfield is controlled by software to select the RNG clock as follows:

00: No clock

01: HSI16

10: SYSCLK

11: PLLQCLK

Bit 25 Reserved, must be kept at reset value.

Bit 24 TIM15SEL: TIM15 clock source selection

(1)

This bit is set and cleared by software. It selects TIM15 clock source as follows:

0: TIMPCLK

1: PLLQCLK

Bit 23 Reserved, must be kept at reset value.

Bit 22 TIM1SEL: TIM1 clock source selection

This bit is set and cleared by software. It selects TIM1 clock source as follows:

0: TIMPCLK

1: PLLQCLK

(1)

Bits 21:20 LPTIM2SEL[1:0]: LPTIM2 clock source selection

This bitfield is controlled by software to select LPTIM2 clock source as follows:

00: PCLK

01: LSI

10: HSI16

11: LSE

Loading...

Loading...