Voltage reference buffer (VREFBUF) RM0444

442/1390 RM0444 Rev 5

17 Voltage reference buffer (VREFBUF)

17.1 Introduction

The devices embed a voltage reference buffer which can be used as voltage reference for

ADC, DAC and also as voltage reference for external components through the VREF+ pin.

When the VREF+ pin is double-bonded with VDDA pin in a package, the voltage reference

buffer is not available and must be kept disabled (refer to datasheet for packages pinout

description).

17.2 VREFBUF functional description

The internal voltage reference buffer supports two voltages

(a)

, which are configured with

VRS bits in the VREFBUF_CSR register:

• VRS = 0: V

REF_OUT1

around 2.048 V.

• VRS = 1: V

REF_OUT2

around 2.5 V.

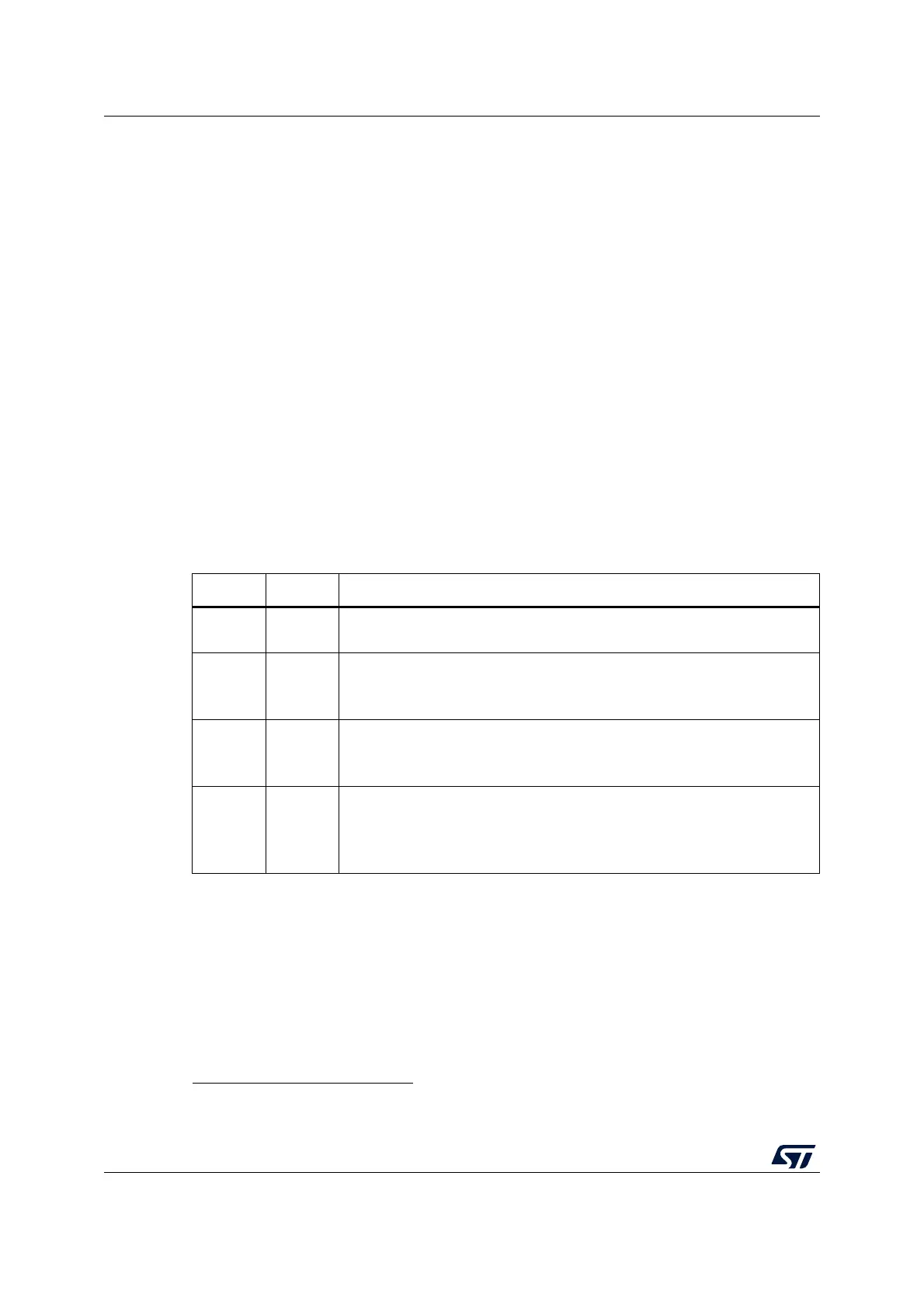

The internal voltage reference can be configured in four different modes depending on

ENVR and HIZ bits configuration. These modes are provided in the table below:

After enabling the VREFBUF by setting ENVR bit and clearing HIZ bit in the VREFBUF_CSR register,

the user must wait until VRR bit is set, meaning that the voltage reference output has reached its

expected value.

a. The minimum V

DDA

voltage depends on VRS setting, refer to the product datasheet.

Table 88. VREF buffer modes

ENVR HIZ VREF buffer configuration

00

VREFBUF buffer off:

–V

REF+

pin pulled-down to V

SSA

01

External voltage reference mode (default value):

– VREFBUF buffer off

–V

REF+

pin input mode

10

Internal voltage reference mode:

– VREFBUF buffer ON

–V

REF+

pin connected to VREFBUF buffer output

11

Hold mode:

– VREFBUF buffer off

–V

REF+

pin floating. The voltage is held with the external capacitor

– VRR detection disabled and VRR bit keeps last state

Loading...

Loading...