Interconnect matrix RM0444

270/1390 RM0444 Rev 5

9 Interconnect matrix

9.1 Introduction

Several peripherals have direct connections between them.

This allows autonomous communication and/or synchronization between peripherals,

saving CPU resources thus power consumption.

In addition, these hardware connections remove software latency and allow design of

predictable systems.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power

run, Low-power sleep, Stop 0, and Stop 1 modes.

For availability of peripherals on different STM32G0x1 products, refer to Section 1.4:

Availability of peripherals.

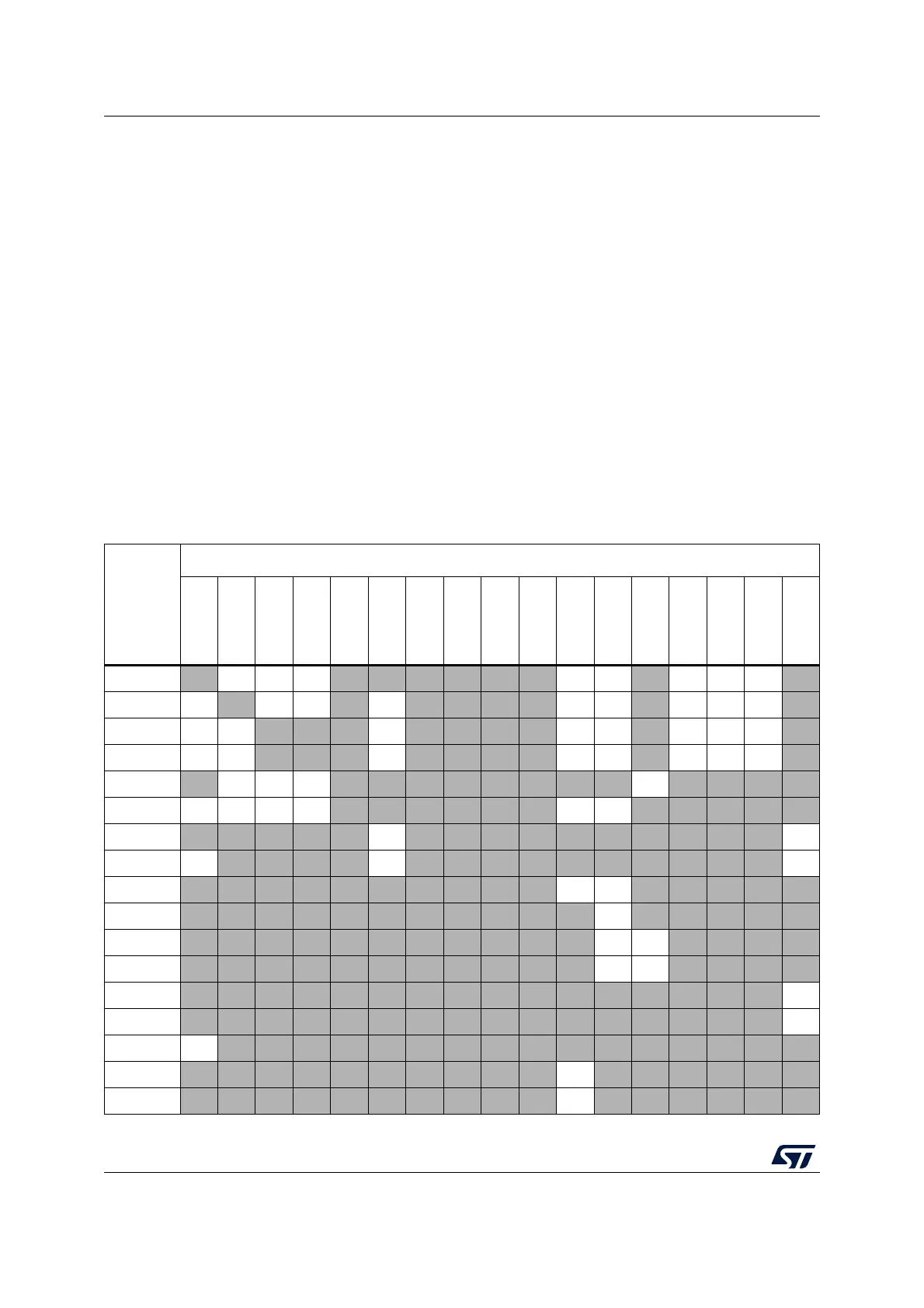

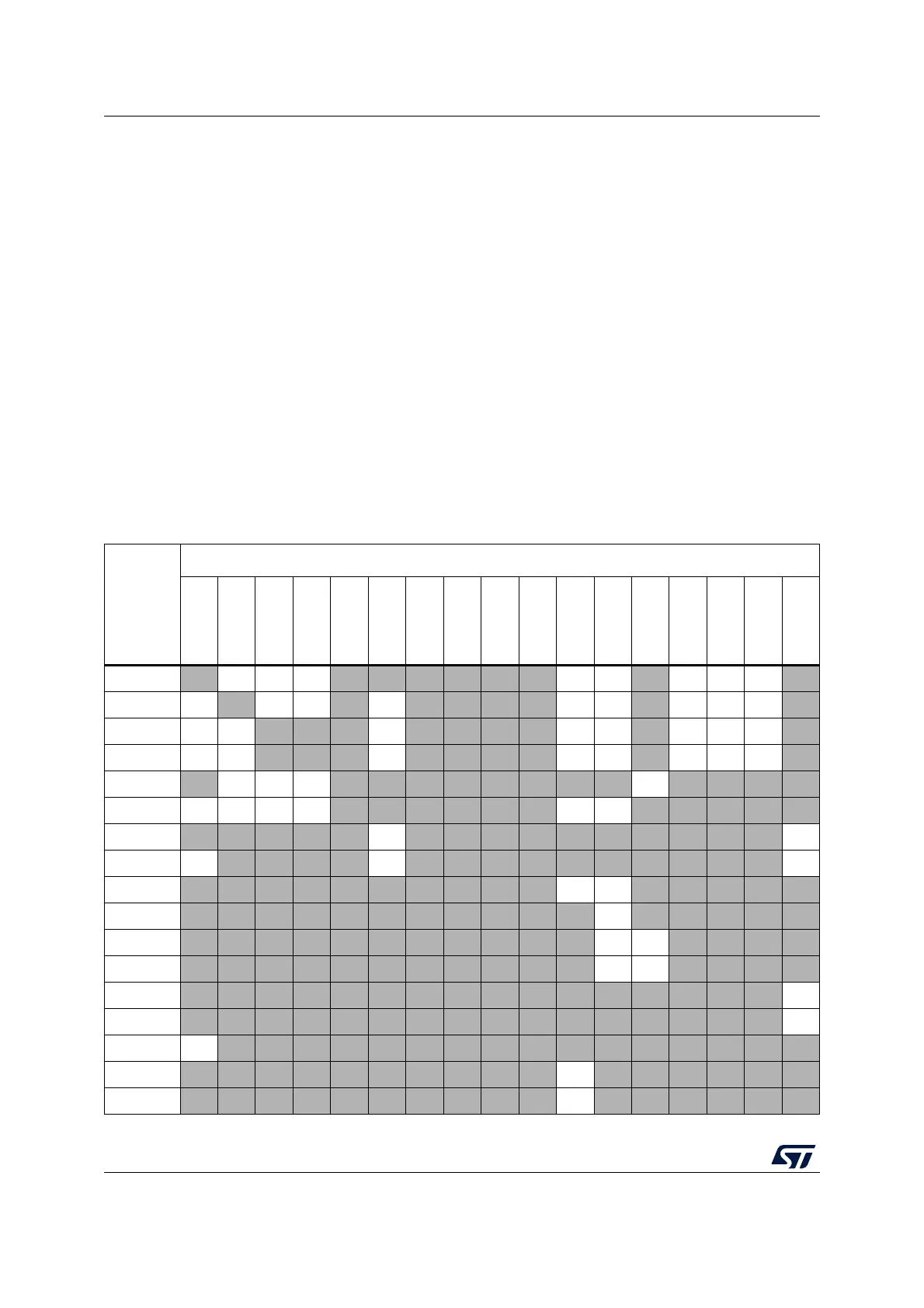

9.2 Connection summary

Table 45. Interconnect matrix

(1)(2)

Source

Destination

TIM1

TIM2

TIM3

TIM4

TIM14

TIM15

TIM16

TIM17

LPTIM1

LPTIM2

ADC

DAC

DMAMUX

COMP1

COMP2

COMP3

IRTIM

TIM1

- 9.3.1 9.3.1 9.3.1 - - - - - - 9.3.2 9.3.4 - 9.3.7 9.3.7 9.3.7 -

TIM2

9.3.1 - 9.3.1 9.3.1 - 9.3.1 - - - - 9.3.2 9.3.4 - 9.3.7 9.3.7 9.3.7 -

TIM3

9.3.1 9.3.1 - - - 9.3.1 - - - - 9.3.2 9.3.4 - 9.3.7 9.3.7 9.3.7 -

TIM4

9.3.1 9.3.1 - - - 9.3.1 - - - - 9.3.2 9.3.4 - 9.3.7 9.3.7 9.3.7 -

TIM14

- 9.3.1 9.3.1 9.3.1 - - - - - - - - 9.3.12 - - - -

TIM15

9.3.1 9.3.1 9.3.1 9.3.1 - - - - - - 9.3.2 9.3.4 - - - - -

TIM16

- - - - - 9.3.1 - - - - - - - - - - 9.3.11

TIM17

9.3.1 - - - - 9.3.1 - - - - - - - - - - 9.3.11

TIM6

- - - - - - - - - - 9.3.2 9.3.4 - - - - -

TIM7

- - - - - - - - - - - 9.3.4 - - - - -

LPTIM1

- - - - - - - - - - - 9.3.4 9.3.12 - - - -

LPTIM2

- - - - - - - - - - - 9.3.4 9.3.12 - - - -

USART1

- - - - - - - - - - - - - - - - 9.3.11

USART4

- - - - - - - - - - - - - - - - 9.3.11

ADC

9.3.3 - - - - - - - - - - - - - - - -

T. sensor

- - - - - - - - - - 9.3.8 - - - - - -

VBAT

- - - - - - - - - - 9.3.8 - - - - - -

Loading...

Loading...