RM0444 Rev 5 1377/1390

RM0444 Debug support (DBG)

1378

40.10.5 DBG register map

The following table summarizes the Debug registers.

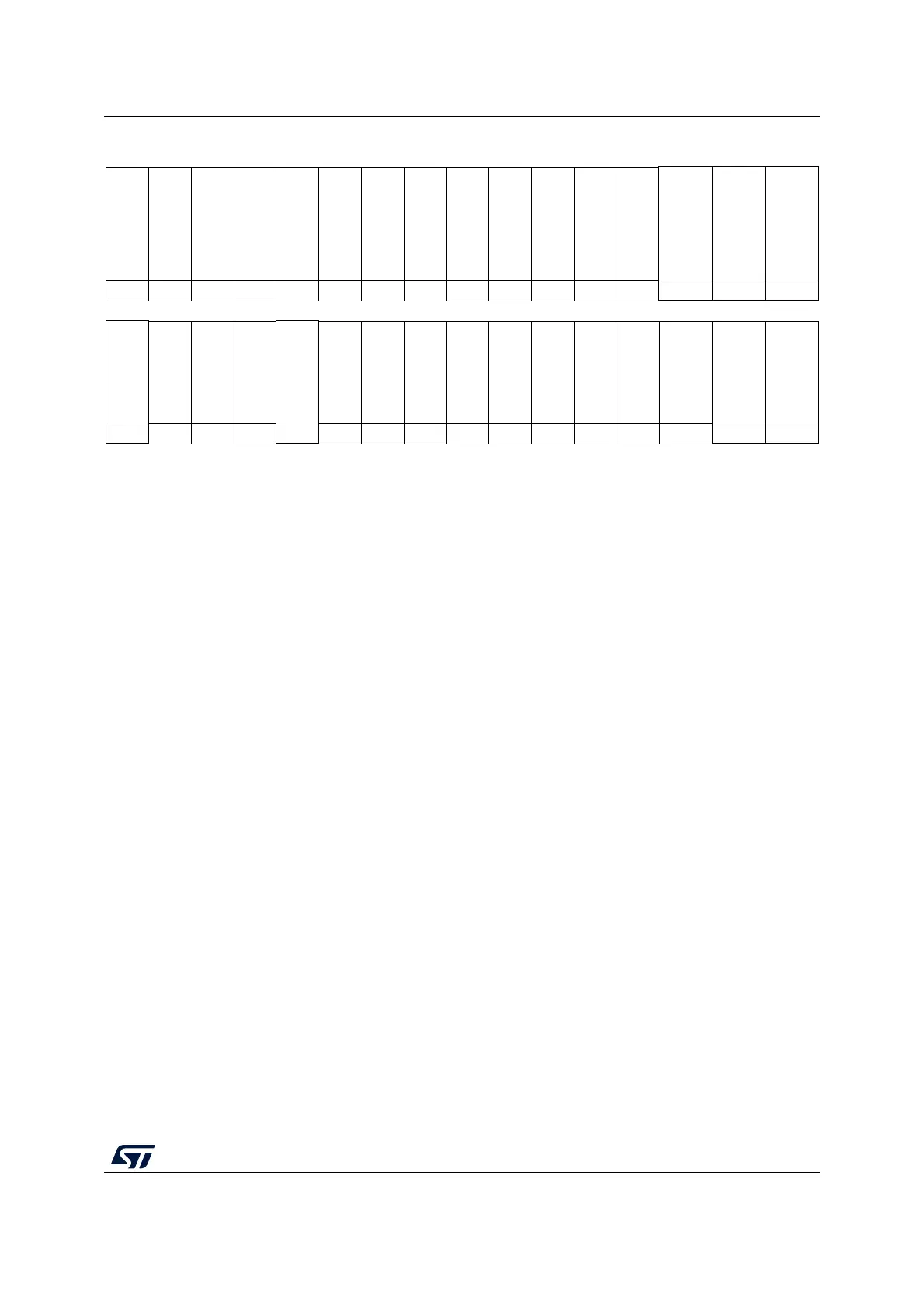

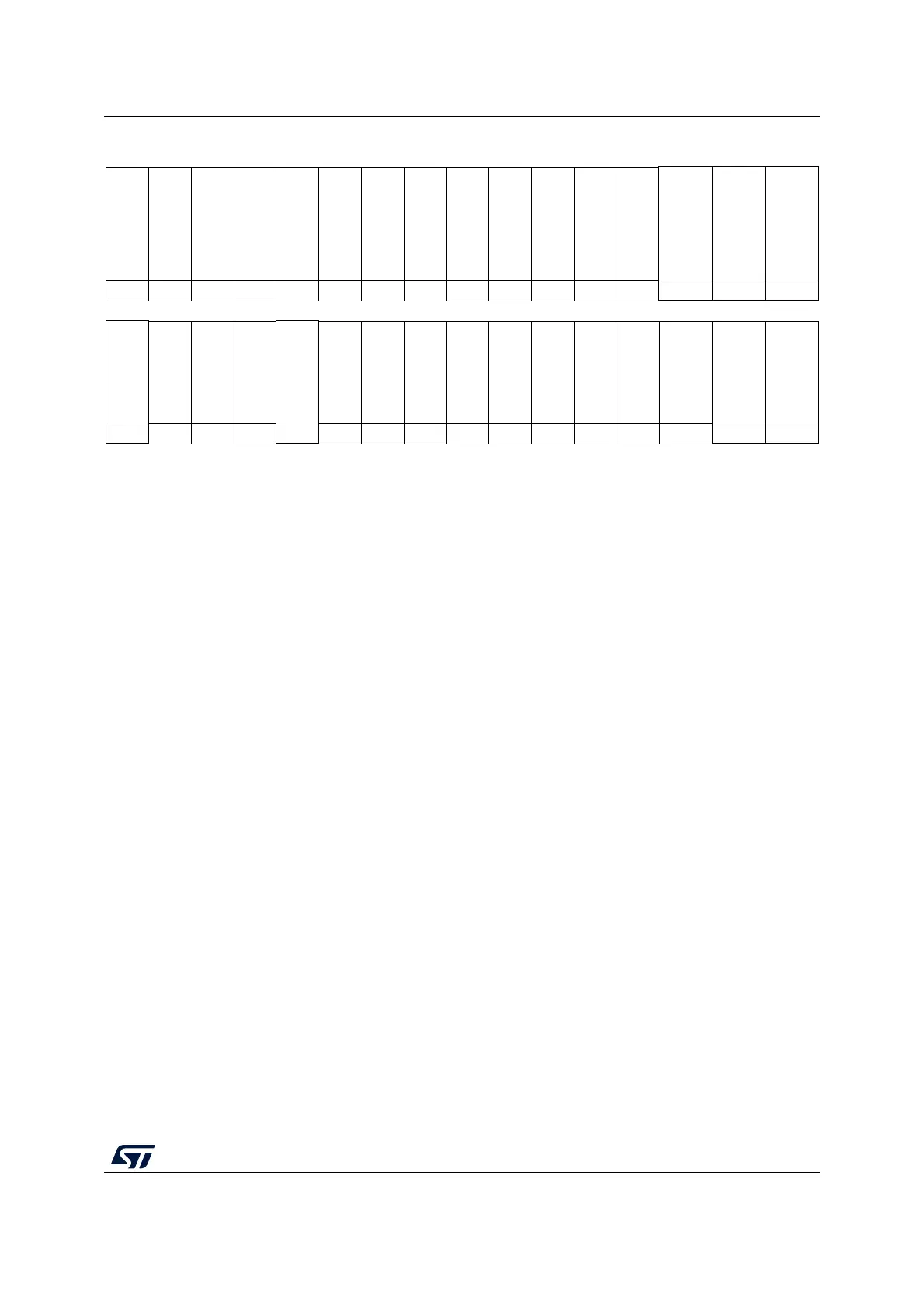

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

DBG_TIM17_STOP

DBG_TIM16_STOP

DBG_TIM15_STOP

(1)

rw rw rw

1514131211109876543 2 1 0

DBG_TIM14_STOP

Res.

Res.

Res.

DBG_TIM1_STOP

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

rw rw

1. Only significant on devices integrating TIM15, otherwise reserved. Refer to Section 1.4: Availability of peripherals

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 DBG_TIM17_STOP: Clocking of TIM17 counter when the core is halted

This bit enables/disables the clock to the counter of TIM17 when the core is halted:

0: Enable

1: Disable

Bit 17 DBG_TIM16_STOP: Clocking of TIM16 counter when the core is halted

This bit enables/disables the clock to the counter of TIM16 when the core is halted:

0: Enable

1: Disable

Bit 16 DBG_TIM15_STOP: Clocking of TIM15 counter when the core is halted

This bit enables/disables the clock to the counter of TIM15 when the core is halted:

0: Enable

1: Disable

Bit 15 DBG_TIM14_STOP: Clocking of TIM14 counter when the core is halted

This bit enables/disables the clock to the counter of TIM14 when the core is halted:

0: Enable

1: Disable

Bits 14:12 Reserved, must be kept at reset value.

Bit 11 DBG_TIM1_STOP: Clocking of TIM1 counter when the core is halted

This bit enables/disables the clock to the counter of TIM1 when the core is halted:

0: Enable

1: Disable

Bits 10:0 Reserved, must be kept at reset value.

Loading...

Loading...