HDMI-CEC controller (CEC) RM0444

1358/1390 RM0444 Rev 5

39.7.2 CEC configuration register (CEC_CFGR)

This register is used to configure the HDMI-CEC controller.

Address offset: 0x04

Reset value: 0x0000 0000

Caution: It is mandatory to write CEC_CFGR only when CECEN = 0.

Bit 0 CECEN: CEC enable

The CECEN bit is set and cleared by software. CECEN = 1 starts message reception and enables

the TXSOM control. CECEN = 0 disables the CEC peripheral, clears all bits of CEC_CR register

and aborts any on-going reception or transmission.

0: CEC peripheral is off.

1: CEC peripheral is on.

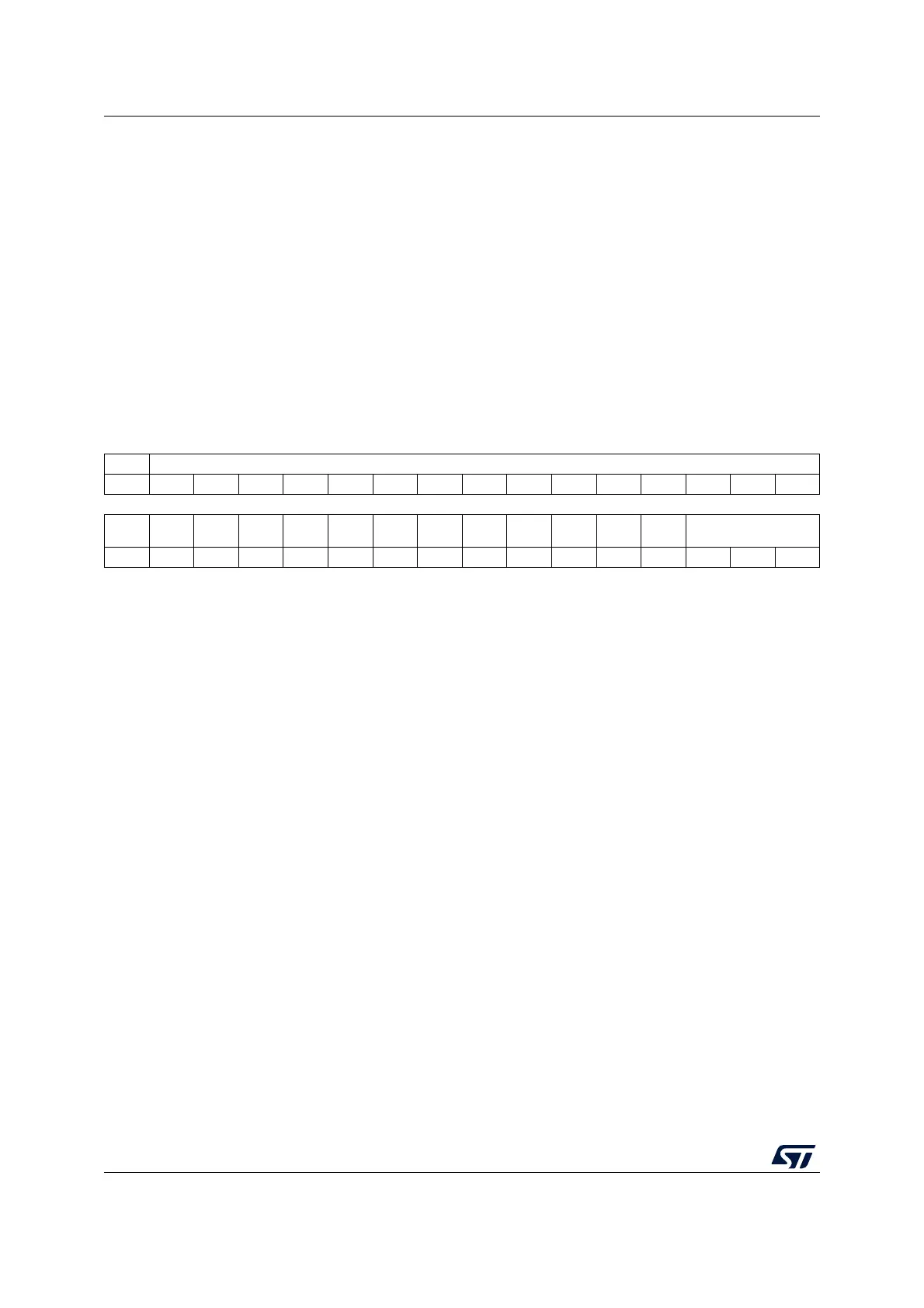

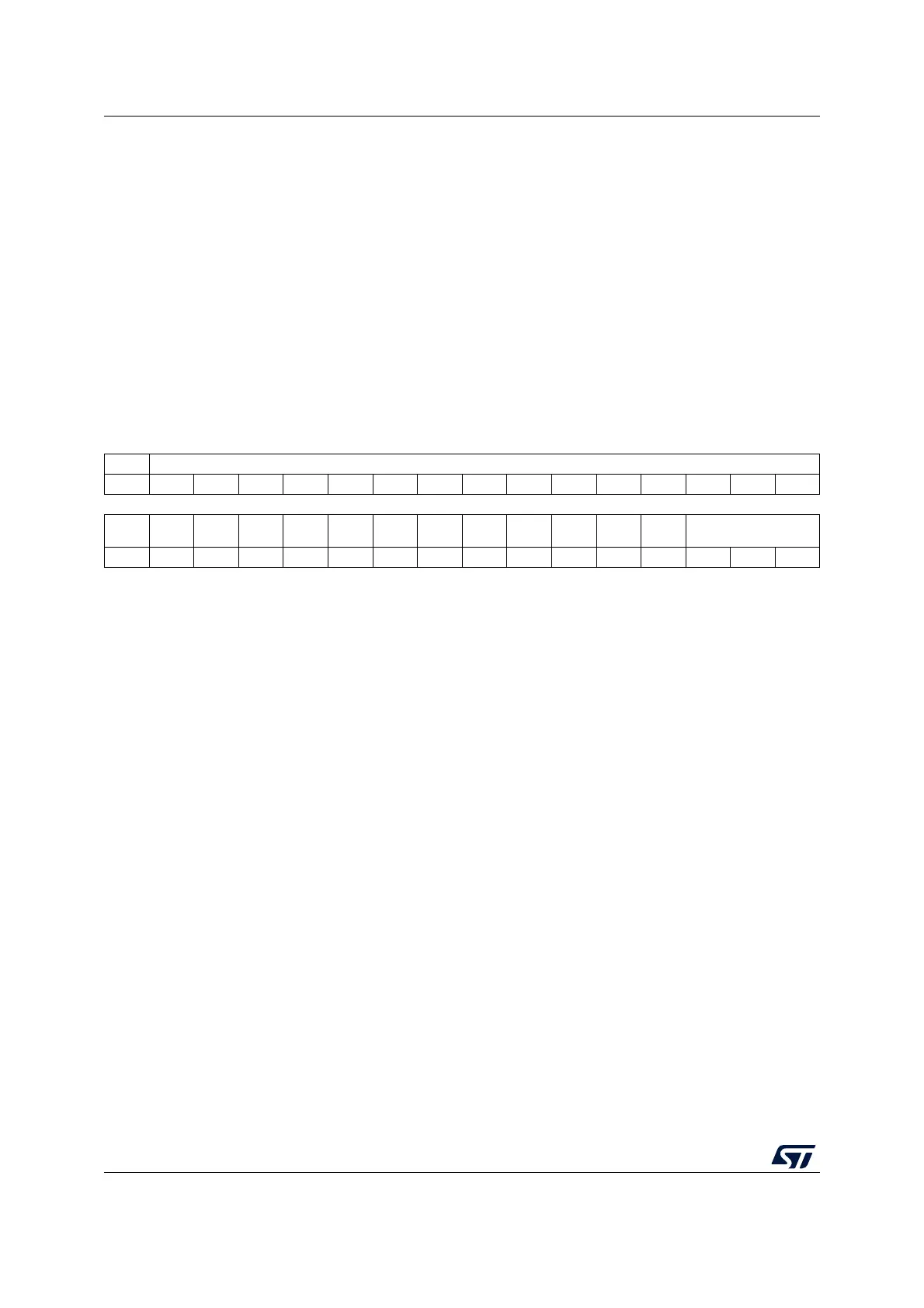

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LSTN OAR[14:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res.

SFT

OP

BRDN

OGEN

LBPE

GEN

BRE

GEN

BRE

STP

RX

TOL

SFT[2:0]

rw rw rw rw rw rw rw rw rw

Bit 31 LSTN: Listen mode

LSTN bit is set and cleared by software.

0: CEC peripheral receives only message addressed to its own address (OAR). Messages

addressed to different destination are ignored. Broadcast messages are always received.

1: CEC peripheral receives messages addressed to its own address (OAR) with positive

acknowledge. Messages addressed to different destination are received, but without interfering with

the CEC bus: no acknowledge sent.

Bits 30:16 OAR[14:0]: Own addresses configuration

The OAR bits are set by software to select which destination logical addresses has to be considered

in receive mode. Each bit, when set, enables the CEC logical address identified by the given bit

position.

At the end of HEADER reception, the received destination address is compared with the enabled

addresses. In case of matching address, the incoming message is acknowledged and received. In

case of non-matching address, the incoming message is received only in listen mode (LSTN = 1),

but without acknowledge sent. Broadcast messages are always received.

Example:

OAR = 0b000 0000 0010 0001 means that CEC acknowledges addresses 0x0 and 0x5.

Consequently, each message directed to one of these addresses is received.

Bits 15:9 Reserved, must be kept at reset value.

Bit 8 SFTOP: SFT option bit

The SFTOPT bit is set and cleared by software.

0: SFT timer starts when TXSOM is set by software.

1: SFT timer starts automatically at the end of message transmission/reception.

Loading...

Loading...