Embedded Flash memory (FLASH) RM0444

102/1390 RM0444 Rev 5

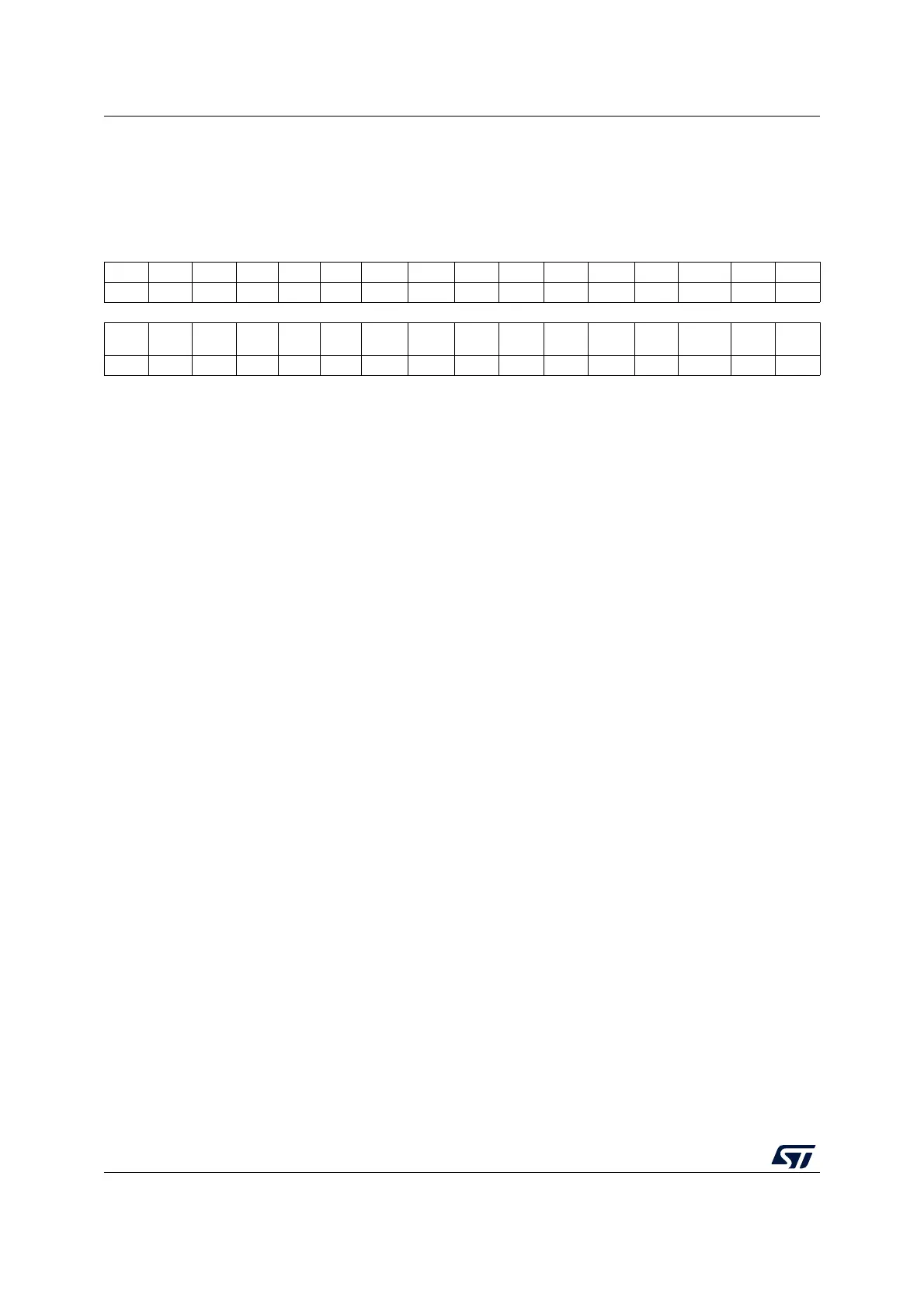

3.7.4 FLASH status register (FLASH_SR)

Address offset: 0x010

Reset value: 0x000X 0000

es

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CFGBSY BSY2 BSY1

rrr

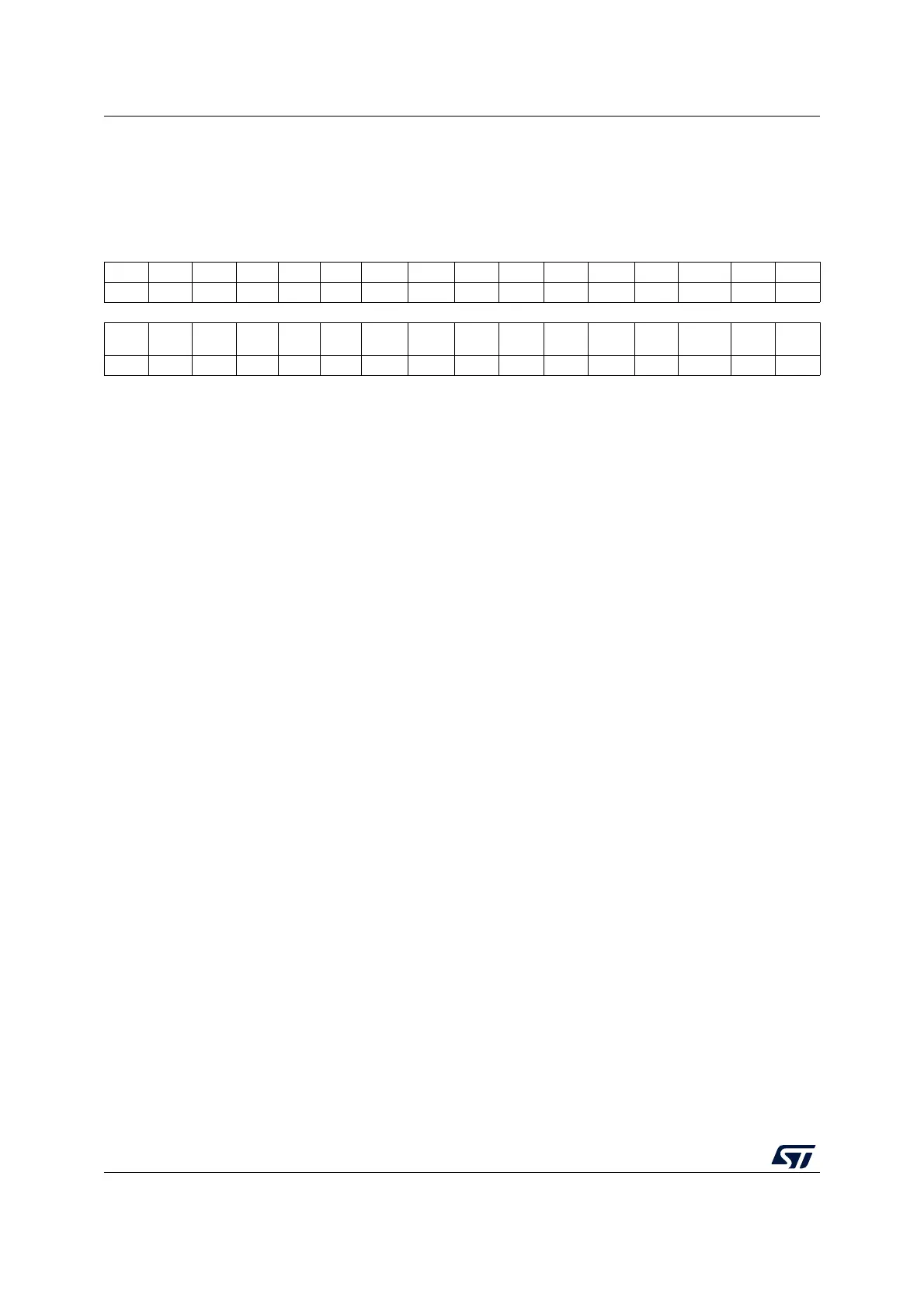

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OPTV

ERR

RD

ERR

Res. Res. Res. Res.

FAST

ERR

MISS

ERR

PGS

ERR

SIZ

ERR

PGA

ERR

WRP

ERR

PROG

ERR

Res.

OP

ERR

EOP

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 CFGBSY: Programming or erase configuration busy.

This flag is set and reset by hardware. (set when first word is sent and reset when program

operation completes or is interrupted by an error.)

When set to 1 the programming and erase settings in PB and PNB bits requested by FLASH

control register (FLASH_CR) are used (busy), and cannot be changed (a programming or

erase operation is ongoing).

When reset to 0 programming and erase settings in PB and PNB bits in FLASH control

register (FLASH_CR) can be modified.

Bit 17 BSY2: Busy

This flag indicates that a Flash memory Bank 2 operation requested by FLASH control

register (FLASH_CR) is in progress. This bit is set at the beginning of the Flash memory

operation, and cleared when the operation finishes or when an error occurs.

Bit 16 BSY1: Busy

This flag indicates that a Flash memory (Bank 1 for dual-bank devices) operation requested

by FLASH control register (FLASH_CR) is in progress. This bit is set at the beginning of the

Flash memory operation, and cleared when the operation finishes or when an error occurs.

Bit 15 OPTVERR: Option and Engineering bits loading validity error

Set by hardware when the options and engineering bits read may not be the one configured

by the user or production. If options and engineering bits haven’t been properly loaded,

OPTVERR is set again after each system reset. Option bytes that fail loading are forced to a

safe value, see Section 3.4.2: FLASH option byte programming.

Cleared by writing 1.

Bit 14 RDERR: PCROP read error

Set by hardware when an address to be read belongs to a read protected area of the Flash

memory (PCROP protection). An interrupt is generated if RDERRIE is set in FLASH_CR.

Cleared by writing 1.

Bits 13:10 Reserved, must be kept at reset value.

Bit 9 FASTERR: Fast programming error

Set by hardware when a fast programming sequence (activated by FSTPG) is interrupted

due to an error (alignment, size, write protection or data miss). The corresponding status bit

(PGAERR, SIZERR, WRPERR or MISSERR) is set at the same time.

Cleared by writing 1.

Loading...

Loading...