Reset and clock control (RCC) RM0444

204/1390 RM0444 Rev 5

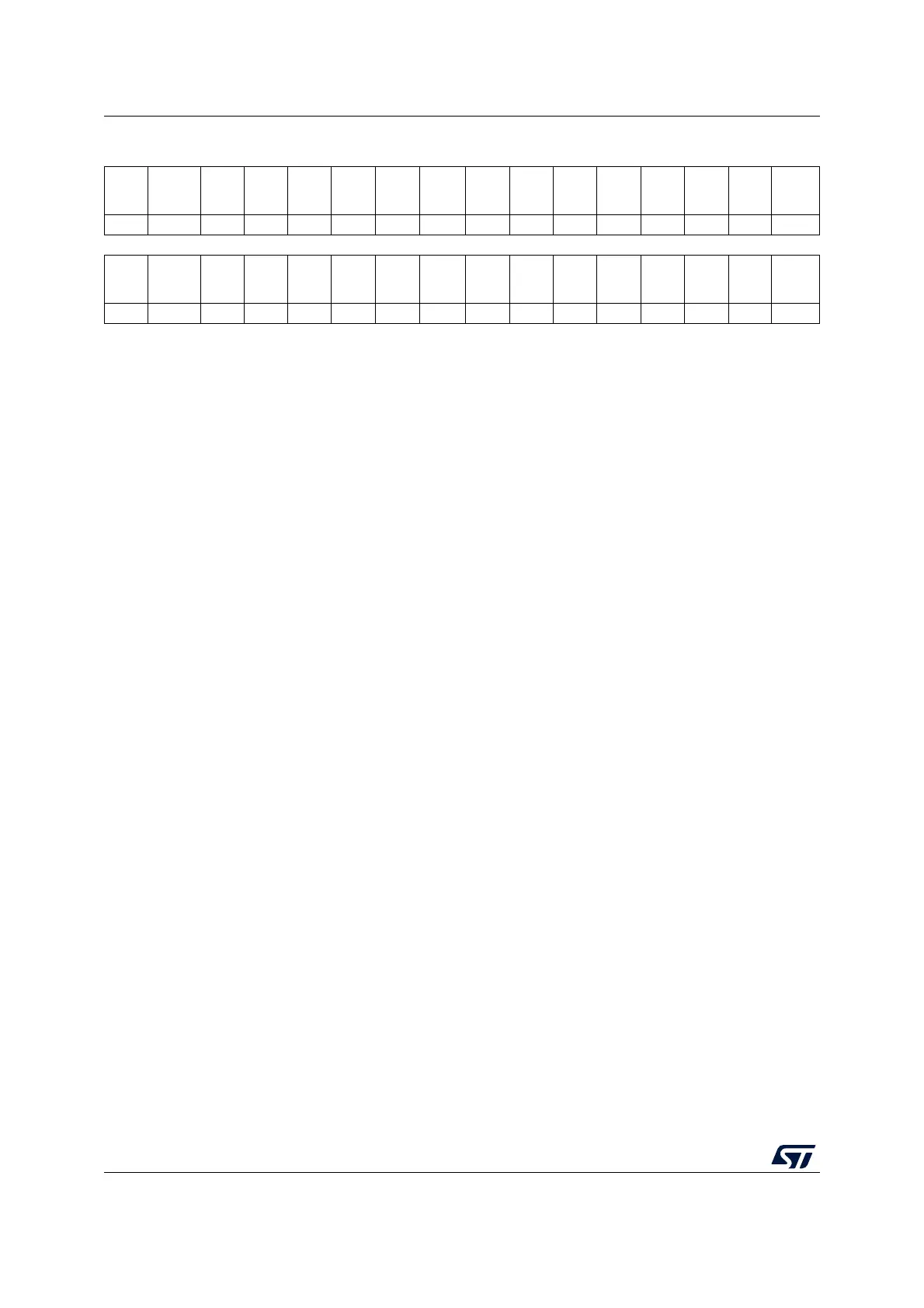

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

RNG

SMEN

(1)

Res.

AES

SMEN

(1)

rw rw

1514131211109 87654321 0

Res. Res. Res.

CRC

SMEN

Res. Res.

SRAM

SMEN

FLASH

SMEN

Res. Res. Res. Res. Res. Res.

DMA2

SMEN

(1)

DMA1

SMEN

rw rw rw rw rw

1. Only significant on devices integrating the corresponding peripheral, otherwise reserved with zero reset value. Refer to

Section 1.4: Availability of peripherals.

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 RNGSMEN: RNG clock enable during Sleep and Stop mode

(1)

Set and cleared by software.

0: Disable

1: Enable

Bits 17 Reserved, must be kept at reset value.

Bit 16 AESSMEN: AES hardware accelerator clock enable during Sleep mode

(1)

Set and cleared by software.

0: Disable

1: Enable

Bits 15:13 Reserved, must be kept at reset value.

Bit 12 CRCSMEN: CRC clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bits 11:10 Reserved, must be kept at reset value.

Bit 9 SRAMSMEN: SRAM clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

Bit 8 FLASHSMEN: Flash memory interface clock enable during Sleep mode

Set and cleared by software.

0: Disable

1: Enable

This bit can be activated only when the Flash memory is in power down mode.

Loading...

Loading...