Embedded Flash memory (FLASH) RM0351

102/1693 DocID024597 Rev 3

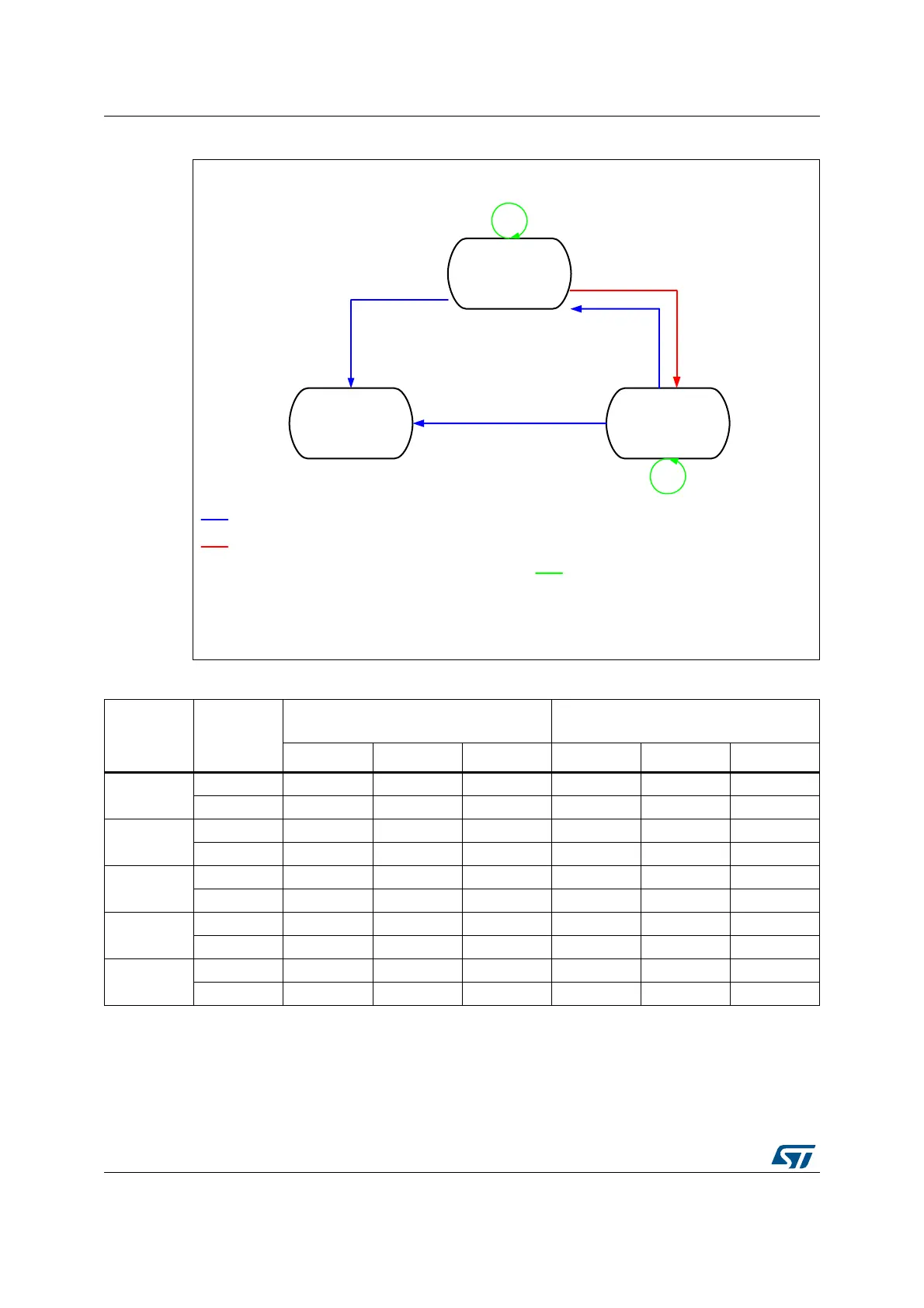

Figure 4. Changing the Read protection (RDP) level

069

2SWLRQVZULWH5'3OHYHOLQFUHDVHLQFOXGHV

2SWLRQVSDJHHUDVH

1HZRSWLRQVSURJUDP

5'3[$$DQG5'3[&&

2WKHUVRSWLRQVPRGLILHG

:ULWHRSWLRQVLQFOXGLQJ

5'3 [$$

:ULWHRSWLRQV,QFOXGLQJ

5'3 [&&

:ULWHRSWLRQVLQFOXGLQJ

5'3[&&DQG5'3[$$

/HYHO

5'3[$$

5'3[&&

GHIDXOW

/HYHO

5'3 [&&

/HYHO

5'3 [$$

5'3 [$$

2WKHUVRSWLRQVPRGLILHG

:ULWHRSWLRQVLQFOXGLQJ

5'3 [&&

2SWLRQVZULWH5'3OHYHOGHFUHDVHLQFOXGHV

)XOO0DVVHUDVHRU3DUWLDO0DVVHUDVHWRQRW

HUDVH3&523SDJHVLI3&523B5'3LVFOHDUHG

%DFNXSUHJLVWHUVDQG65$0HUDVH

2SWLRQVSDJHHUDVH

1HZRSWLRQVSURJUDP

2SWLRQVZULWH5'3OHYHOLGHQWLFDOLQFOXGHV

2SWLRQVSDJHHUDVH

1HZRSWLRQVSURJUDP

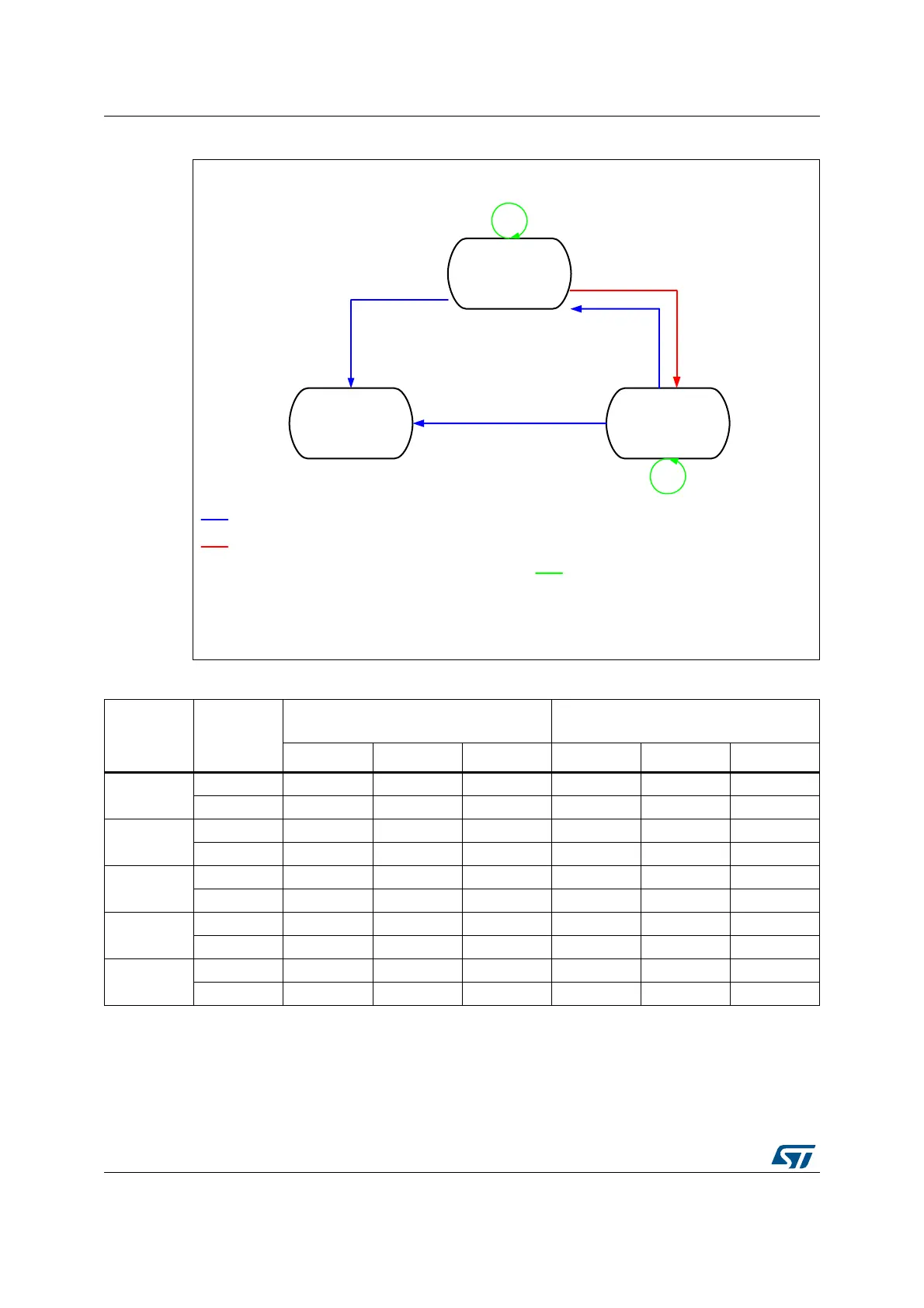

Table 12. Access status versus protection level and execution modes

Area

Protection

level

User execution (BootFromFlash)

Debug/ BootFromRam/

BootFromLoader

Read Write Erase Read Write Erase

Flash main

memory

1 Yes Yes Yes N o No No

(3)

2 Yes Yes Yes N/A

(1)

N/A

(1)

N/A

(1)

System

memory

(2)

1 Yes No No Yes No No

2 Yes No No NA

(1)

N/A

(1)

N/A

(1)

Option bytes

1Yes Yes

(3)

Yes Yes Yes

(3)

Yes

2 Yes No No N/A

(1)

N/A

(1)

N/A

(1)

Backup

registers

1 Yes Yes N/A No No No

(4)

2Yes YesN/A N/A

(1)

N/A

(1)

N/A

(1)

SRAM2

1 Yes Yes N/A No No No

(5)

2Yes YesN/A N/A

(1)

N/A

(1)

N/A

(1)

1. When the protection level 2 is active, the Debug port, the boot from RAM and the boot from system memory are disabled.

2. The system memory is only read-accessible, whatever the protection level (0, 1 or 2) and execution mode.

3. The Flash main memory is erased when the RDP option byte is programmed with all level protections disabled (0xAA).

4. The backup registers are erased when RDP changes from level 1 to level 0.

5. The SRAM2 is erased when RDP changes from level 1 to level 0.

Loading...

Loading...