DocID024597 Rev 3 1551/1693

RM0351 USB on-the-go full-speed (OTG_FS)

1644

43.15.18 OTG device IN endpoint transmit FIFO size register

(OTG_DIEPTXFx) (x = 1..5 , where x is the

FIFO_number)

Address offset: 0x104 + (FIFO_number – 1) × 0x04

Reset values:

FIFO_number = 5 :

0x0200 0200 + (5 * 0x200)

43.15.19 Host-mode registers

Bit values in the register descriptions are expressed in binary unless otherwise specified.

Host-mode registers affect the operation of the core in the host mode. Host mode registers

must not be accessed in device mode, as the results are undefined. Host mode registers

can be categorized as follows:

43.15.20 OTG Host configuration register (OTG_HCFG)

Address offset: 0x400

Reset value: 0x0000 0000

This register configures the core after power-on. Do not make changes to this register after

initializing the host.

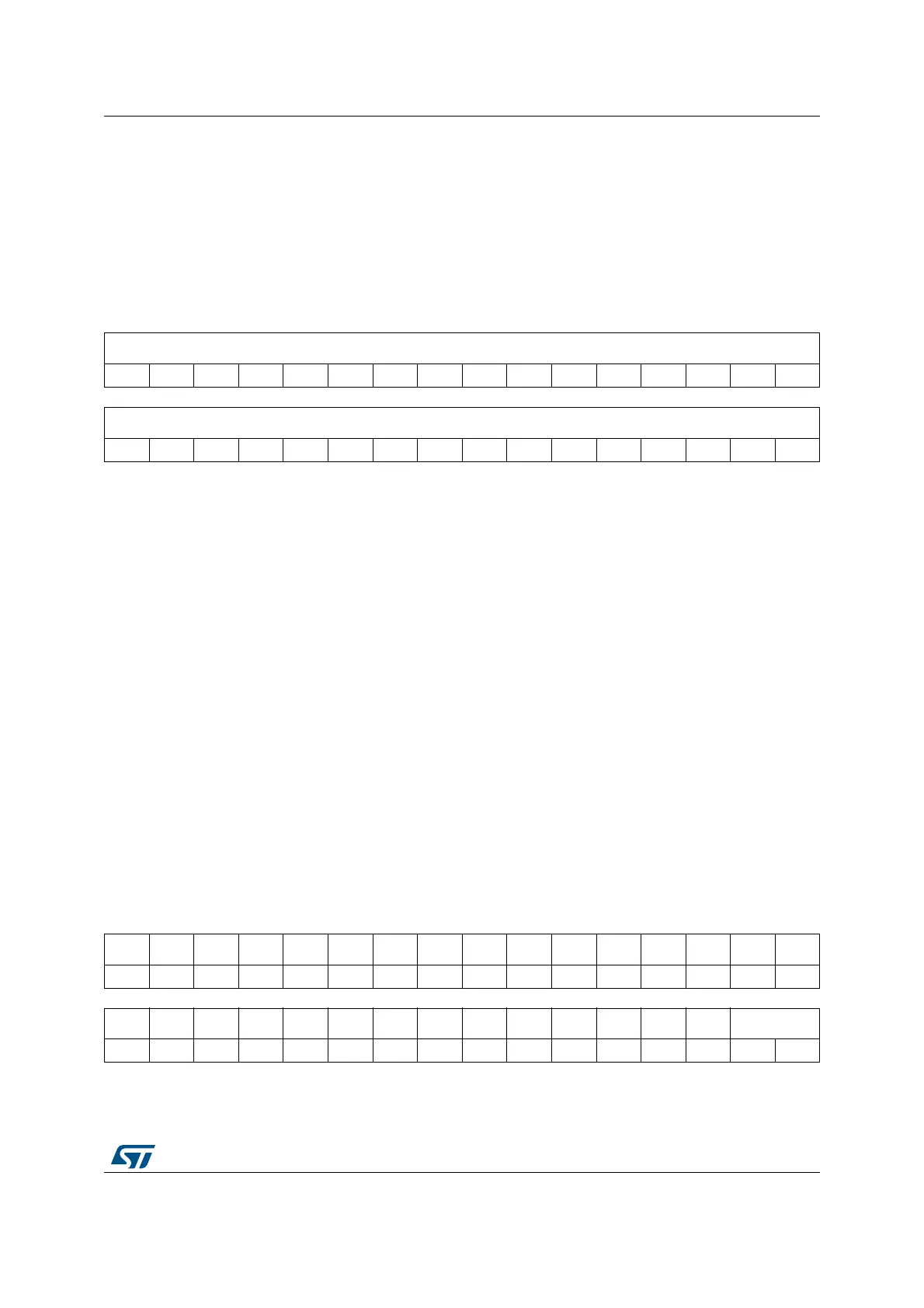

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

INEPTXFD

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

INEPTXSA

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 INEPTXFD: IN endpoint Tx FIFO depth

This value is in terms of 32-bit words.

Minimum value is 16

Bits 15:0 INEPTXSA: IN endpoint FIFOx transmit RAM start address

This field contains the memory start address for IN endpoint transmit FIFOx. The address

must be aligned with a 32-bit memory location.

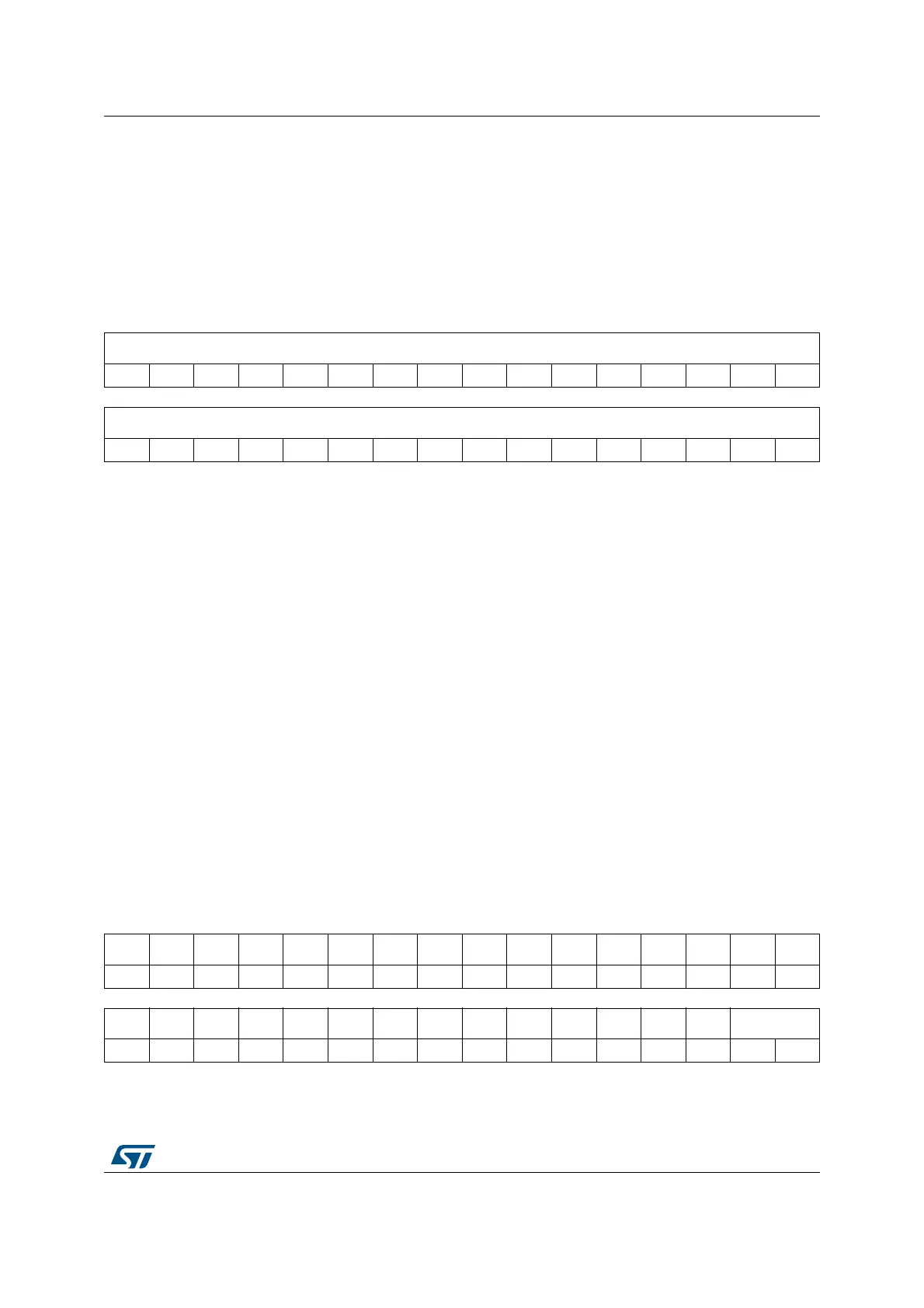

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. FSLSS FSLSPCS

rrwrw

Loading...

Loading...