Direct memory access controller (DMA) RM0351

296/1693 DocID024597 Rev 3

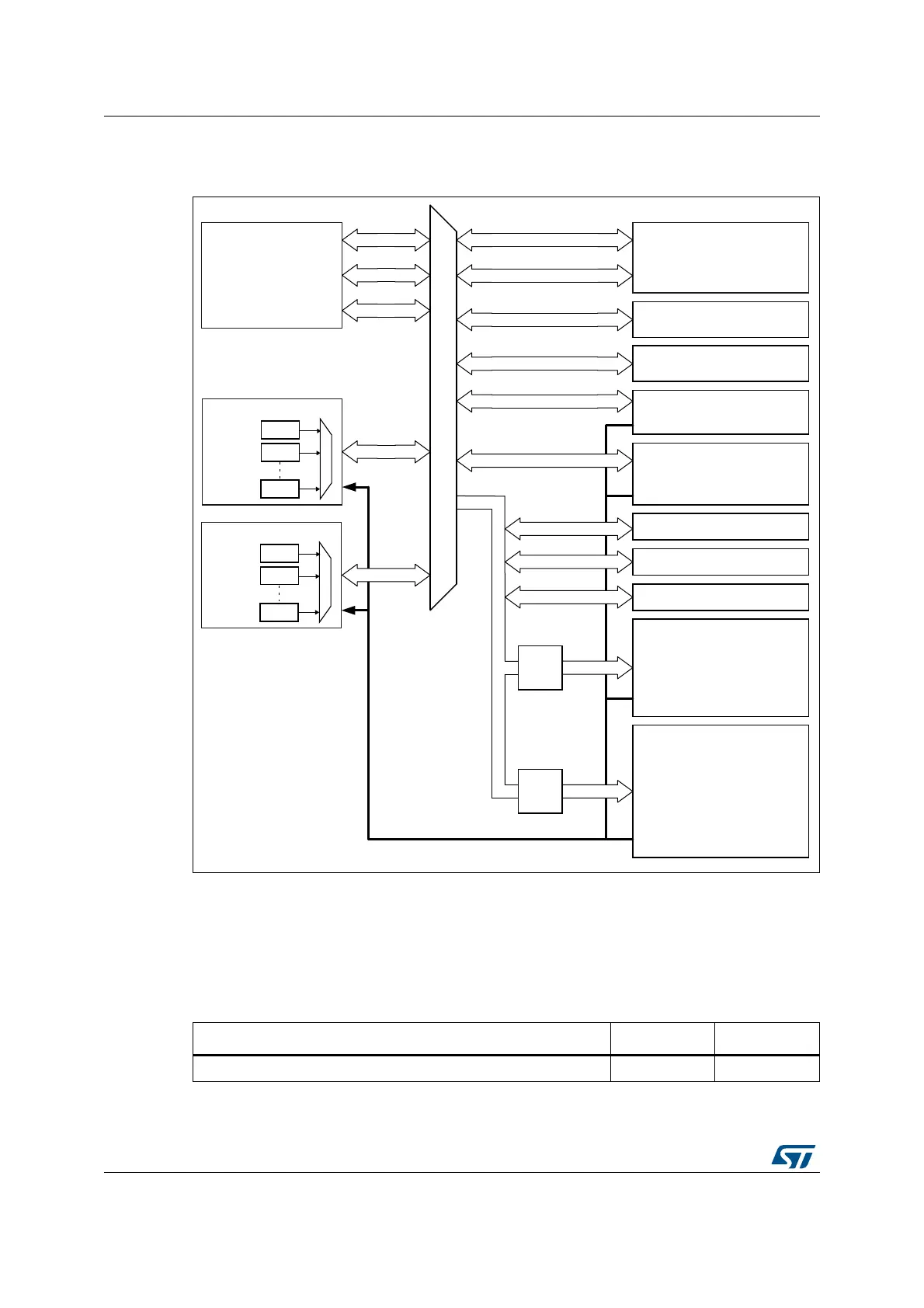

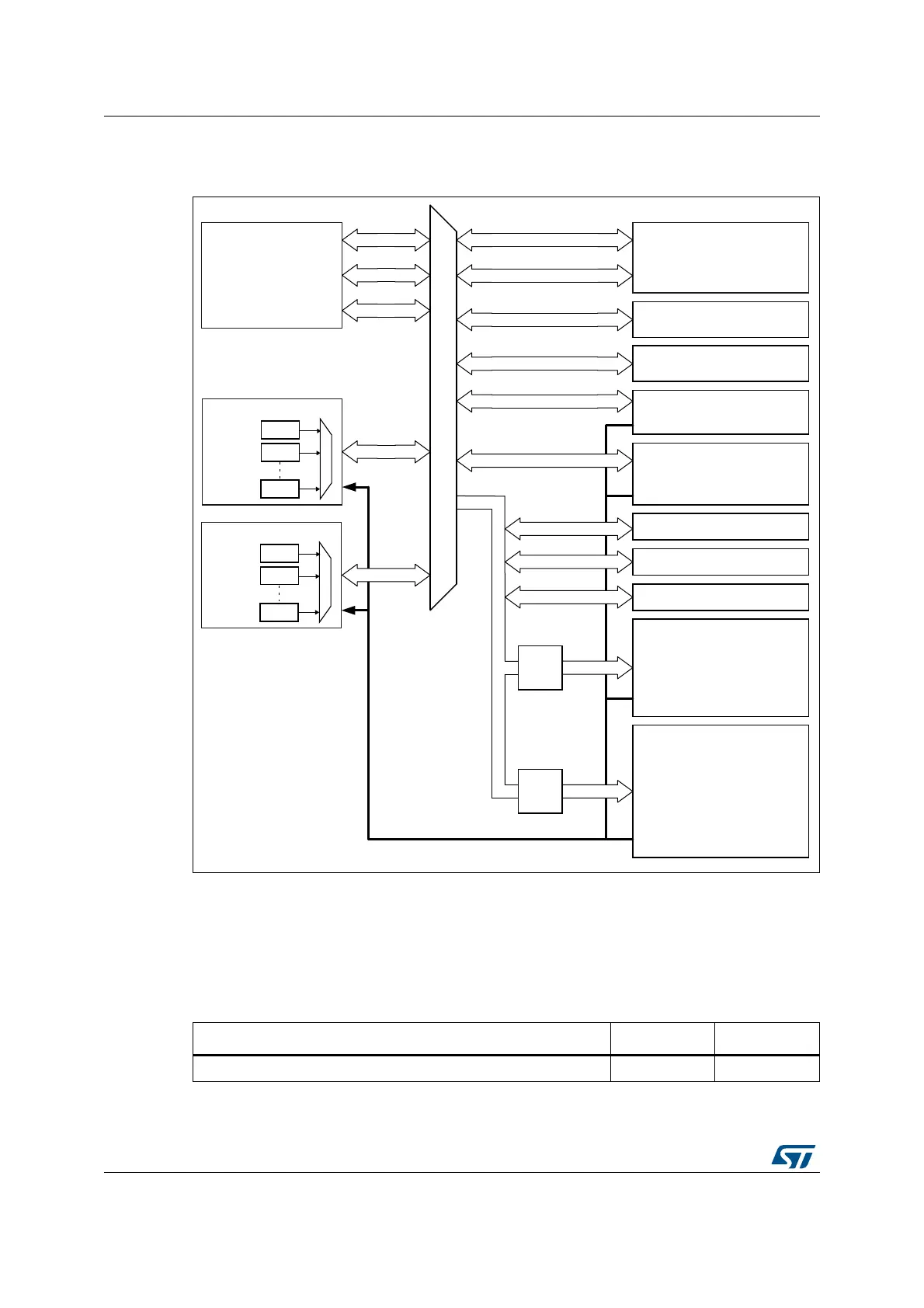

The block diagram is shown in the following figure.

Figure 23. DMA block diagram

10.3 DMA implementation

This manual describes the full set of features implemented in DMA1. DMA2 supports the

same number of channels, and is identical to DMA1.

069

65$0

&K

&K

&K

'0$

'0$UHTXHVWV

5HVHWFORFNFRQWURO5&&

&RUWH[

0ZLWK)38

)ODVKLQWHUIDFH

$3%SHULSKHUDOV

ZLWK'0$FDSDELOLW\

')6'06$,6$,7,0

7,07,07,07,0

86$5763,6'00&

$3%SHULSKHUDOV

ZLWK'0$FDSDELOLW\

6:30,/38$57'$&

'$&,&,&,&

86$5786$578$57

8$5763,63,7,0

7,07,07,07,07,0

)0&DQG4XDG63,

$+%SHULSKHUDOV

ZLWK'0$FDSDELOLW\

$(6$'&$'&$'&

&5&

6EXV

'EXV

,EXV

76&

65$0

$+%

%ULGJH

$3%

$3%

,&RGH

'&RGH

%ULGJH

'0$

&K

&K

&K

'0$

%XVPDWUL[

'0$

Table 36. DMA implementation

Feature DMA1 DMA2

Number of DMA channels 7 7

Loading...

Loading...