DocID024597 Rev 3 1327/1693

RM0351 Serial audio interface (SAI)

1362

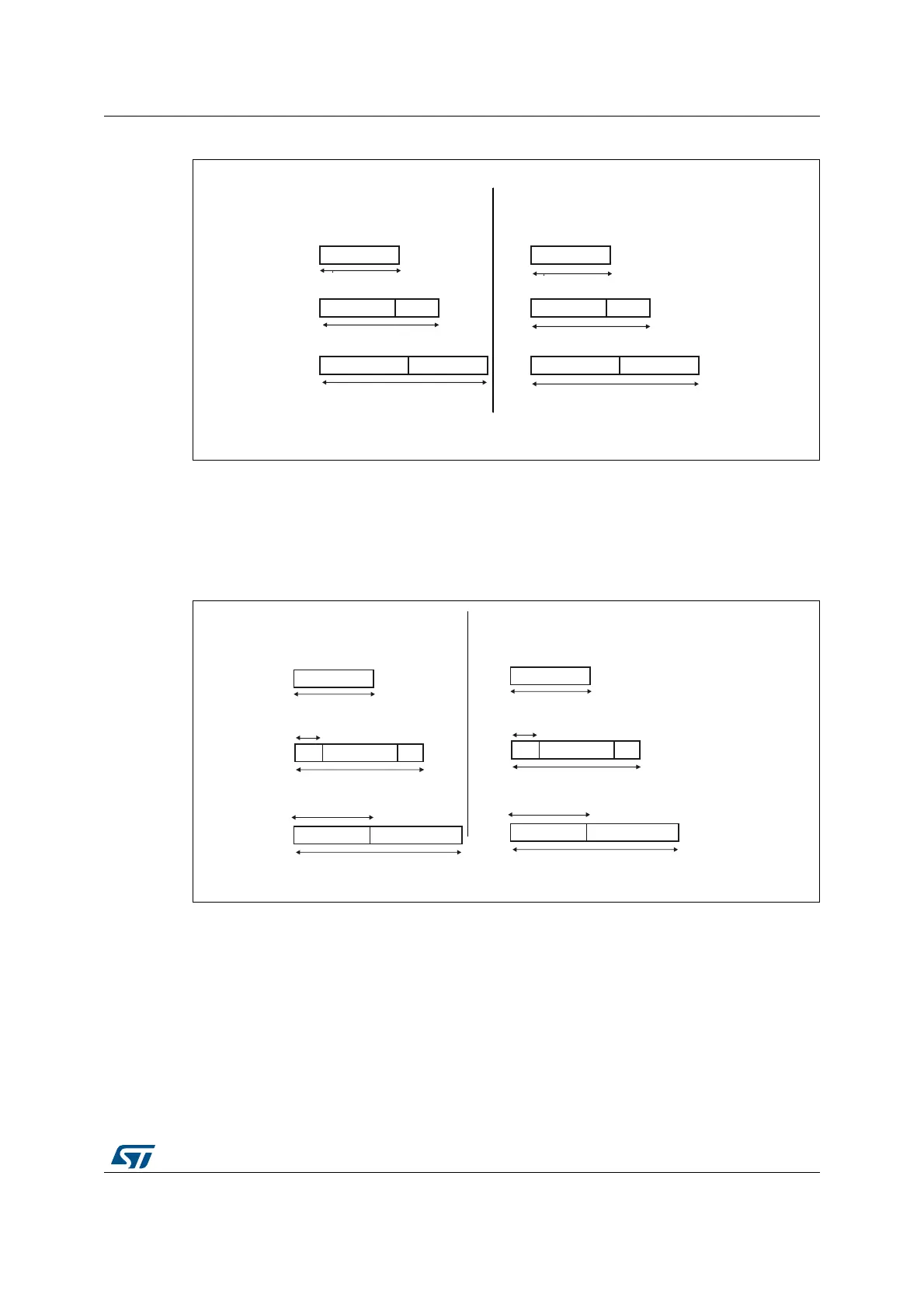

Figure 440. Slot size configuration with FBOFF = 0 in SAI_xSLOTR

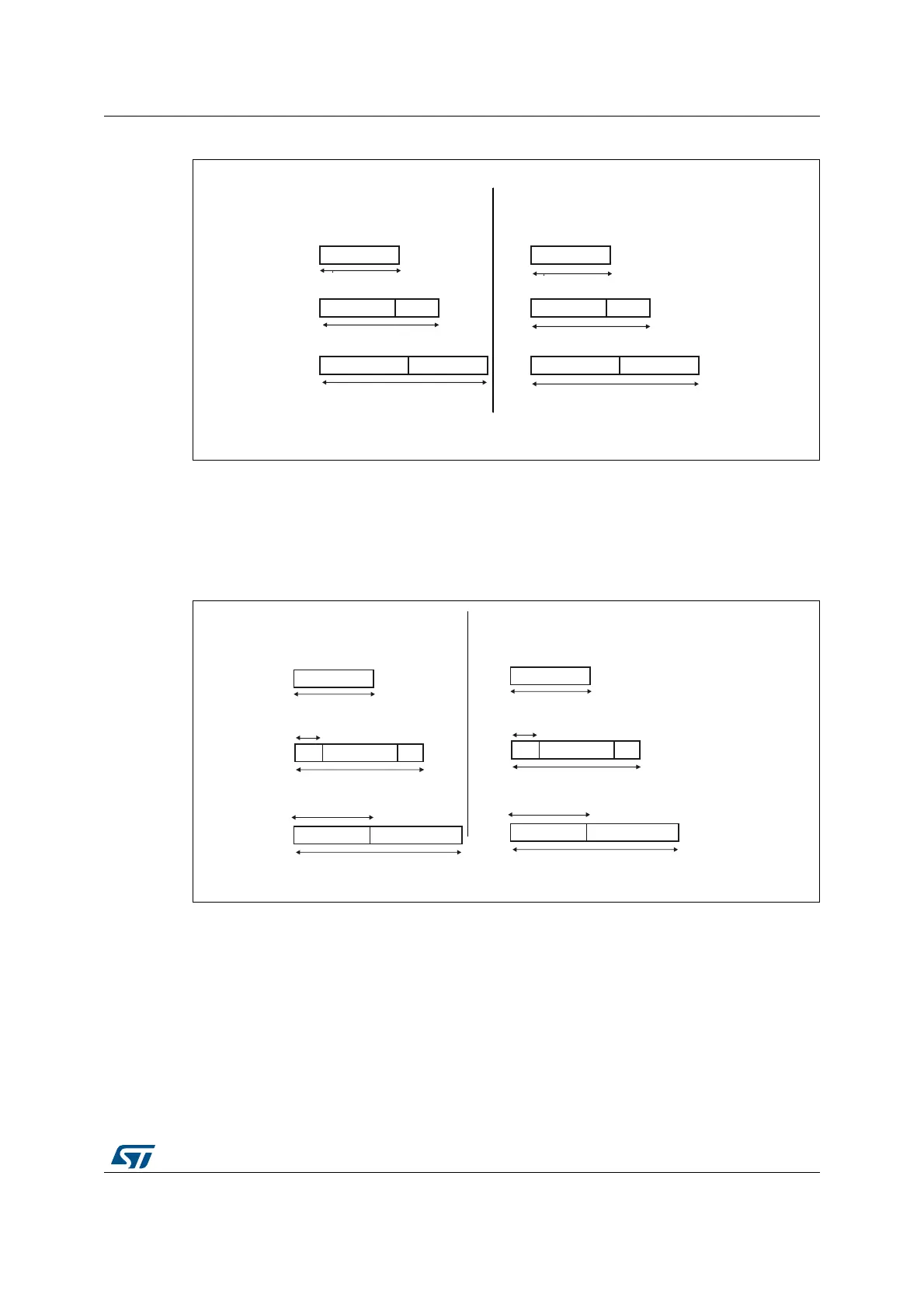

It is possible to choose the position of the first data bit to transfer within the slots. This offset

is configured by FBOFF[4:0] bits in the SAI_xSLOTR register. 0 values will be injected in

transmitter mode from the beginning of the slot until this offset position is reached. In

reception, the bit in the offset phase is ignored. This feature targets the LSB justified

protocol (if the offset is equal to the slot size minus the data size).

Figure 441. First bit offset

It is mandatory to respect the following conditions to avoid bad SAI behavior:

FBOFF ≤ (SLOTSZ - DS),

DS ≤ SLOTSZ,

NBSLOT x SLOTSZ ≤ FRL (frame length),

The number of slots must be even when bit FSDEF in the SAI_xFRCR register is set.

In AC’97 and SPDIF protocol (bit PRTCFG[1:0] = 10 or PRTCFG[1:0] = 01), the slot size is

automatically set as defined in Section 39.3.9: AC’97 link controller.

069

;;

;; ;;

;GRQ¶WFDUH

$XGLREORFNLVWUDQVPLWWHU

6ORWVL]H GDWDVL]H

GDWDVL]H

GDWDVL]H

GDWDVL]H

GDWDVL]H

VORW[

VORW[

VORW[

ELW

ELW

$XGLREORFNLVUHFHLYHU

6ORWVL]H GDWDVL]H

GDWDVL]H

GDWDVL]H

GDWDVL]H

VORW[

VORW[

VORW[

ELW

ELW

GDWDVL]H

069

;;;;

;GRQ¶WFDUH

$XGLREORFNLVWUDQVPLWWHU

6ORWVL]H GDWDVL]H

GDWDVL]H

GDWDVL]H

GDWDVL]H

GDWDVL]H

VORW[

VORW[

VORW[

ELW

ELW

$XGLREORFNLVUHFHLYHU

)%2))

)%2)) 6/276='6

;;

6ORWVL]H GDWDVL]H

GDWDVL]H

GDWDVL]H

GDWDVL]H

GDWDVL]H

VORW[

VORW[

VORW[

ELW

ELW

;;

)%2))

)%2)) 6/276='6

Loading...

Loading...