DocID024597 Rev 3 1667/1693

RM0351 Debug support (DBG)

1678

44.16.4 Debug MCU APB1 freeze register1(DBGMCU_APB1FZR1)

Address: 0xE004 2008

Power on reset (POR): 0x0000 0000

System reset: not affected

Access: Only 32-bit access are supported.

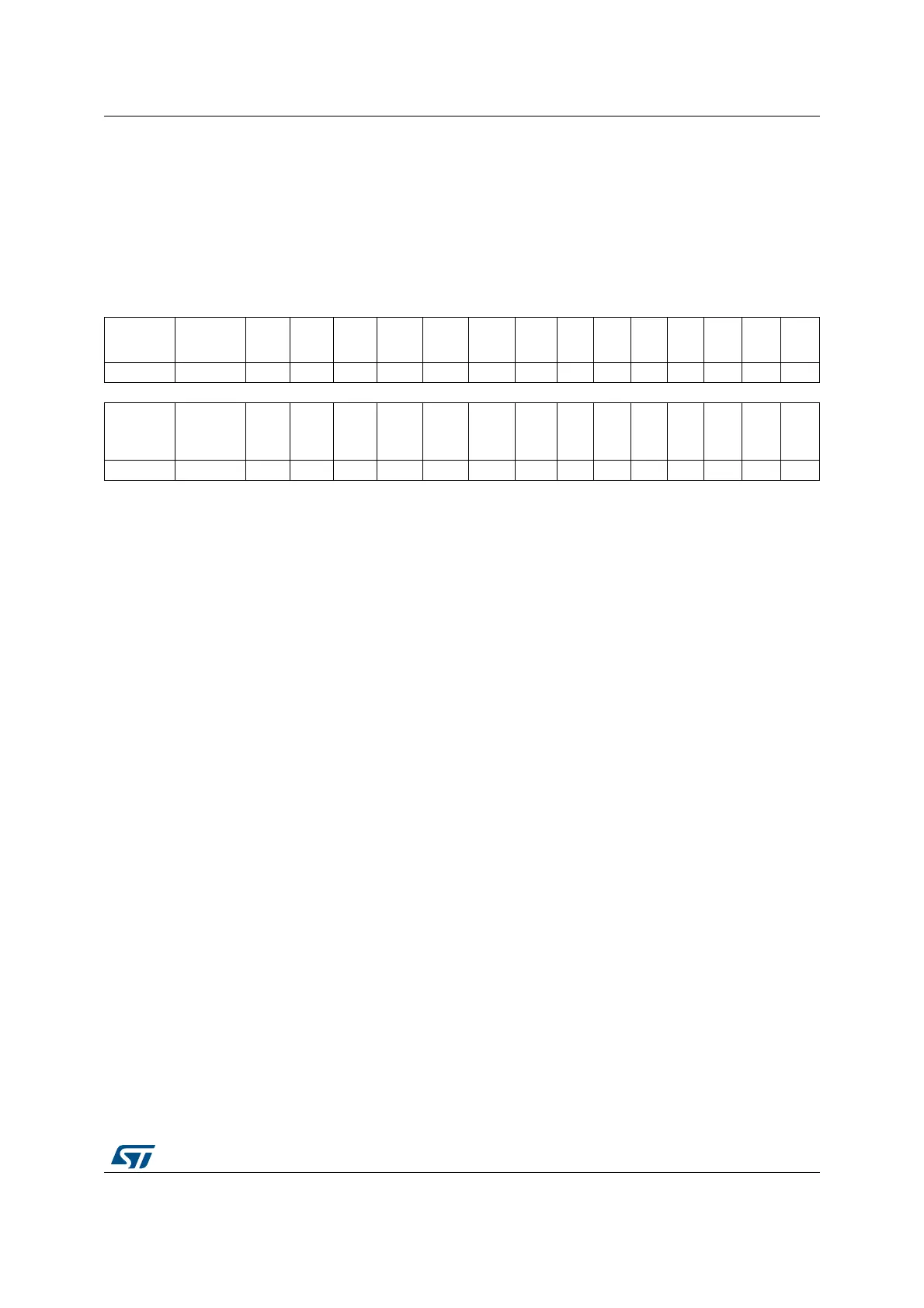

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LPTIM1_

STOP

Res.. Res. Res. Res. Res.

DBG_

CAN_

STOP

Res.

DBG_

I2C3_

STOP

DBG_

I2C2_

STOP

DBG_

I2C1_

STOP

Res. Res. Res. Res. Res.

rw rw rw rw rw

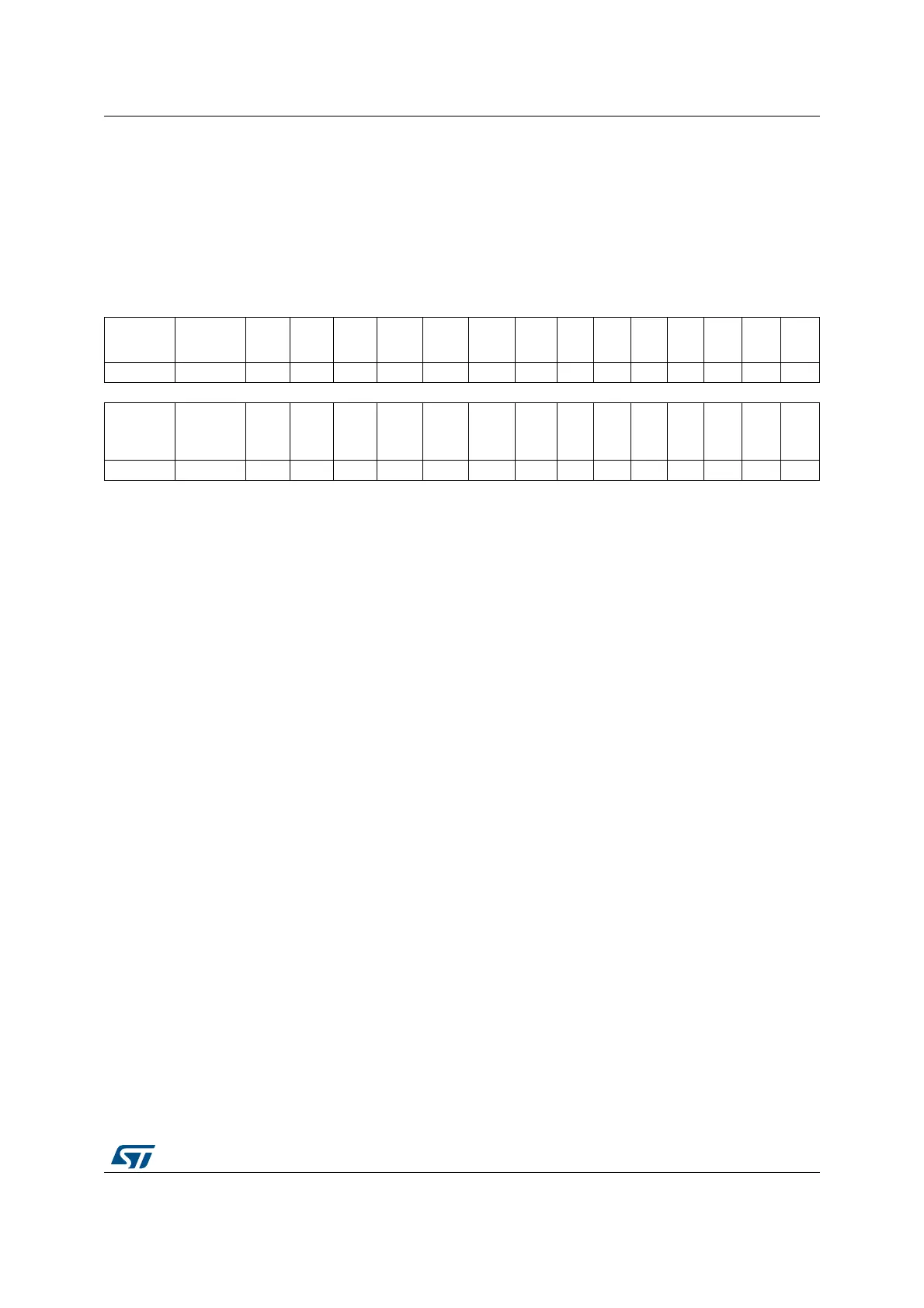

15 14 1312 11 10 9 8 7 65432 1 0

Res. Res. Res.

DBG_

IWDG_

STOP

DBG_

WWDG

_STOP

DBG_

RTC_

STOP

Res. Res. Res. Res.

DBG_

TIM7

_STO

P

DBG_

TIM6

_STO

P

DBG_

TIM5

_STO

P

DBG_

TIM4_

STOP

DBG_

TIM3_

STOP

DBG_

TIM2_

STOP

rw rw rw rw rw rw rw rw rw

Bit 31 DBG_LPTIM1_STOP: LPTIM1 counter stopped when core is halted

0: The counter clock of LPTIM1 is fed even if the core is halted

1: The counter clock of LPTIM1 is stopped when the core is halted

Bits 30:26 Reserved, must be kept at reset value.

Bit 25 DBG_CAN_STOP: bxCAN stopped when core is halted

0: Same behavior as in normal mode

1: The bxCAN receive registers are frozen

Bit 24 Reserved, must be kept at reset value.

Bit 23 DBG_I2C3_STOP: I2C3 SMBUS timeout counter stopped when core is halted

0: Same behavior as in normal mode

1: The I2C3 SMBus timeout is frozen

Bit 22 DBG_I2C2_STOP: I2C2 SMBUS timeout counter stopped when core is halted

0: Same behavior as in normal mode

1: The I2C2 SMBus timeout is frozen

Bit 21 DBG_I2C1_STOP: I2C1 SMBUS timeout counter stopped when core is halted

0: Same behavior as in normal mode

1: The I2C1 SMBus timeout is frozen

Bits 20:13 Reserved, must be kept at reset value.

Bit 12 DBG_IWDG_STOP: Independent watchdog counter stopped when core is halted

0: The independent watchdog counter clock continues even if the core is halted

1: The independent watchdog counter clock is stopped when the core is halted

Bit 11 DBG_WWDG_STOP: Window watchdog counter stopped when core is halted

0: The window watchdog counter clock continues even if the core is halted

1: The window watchdog counter clock is stopped when the core is halted

Bit 10 DBG_RTC_STOP: RTC counter stopped when core is halted

0: The clock of the RTC counter is fed even if the core is halted

1: The clock of the RTC counter is stopped when the core is halted

Bits 9:6 Reserved, must be kept at reset value.

Loading...

Loading...