DocID024597 Rev 3 733/1693

RM0351 Advanced encryption standard hardware accelerator (AES)

751

25.9.3 Mode 3: decryption

1. Disable the AES by resetting the EN bit in the AES_CR register.

2. Configure mode 3 by programming MODE[1:0] = 10 in the AES_CR register and select

which type of chaining mode needs to be performed by programming the CHMOD[2:0]

bits.

3. Select Key length 128-bit or 256-bit via KEYSIZE bits configuration in AES_CR

register.

4. Write the AES_KEYRx registers with the decryption key (this step can be bypassed if

the derivation key is already stored in the AES_KEYRx registers using mode 2: key

derivation). Write the AES_IVRx registers if CTR, CBC or GCM mode is selected. For

ECB mode, the AES_IVRx registers are not used.

5. Enable the AES by setting the EN bit in the AES_CR register.

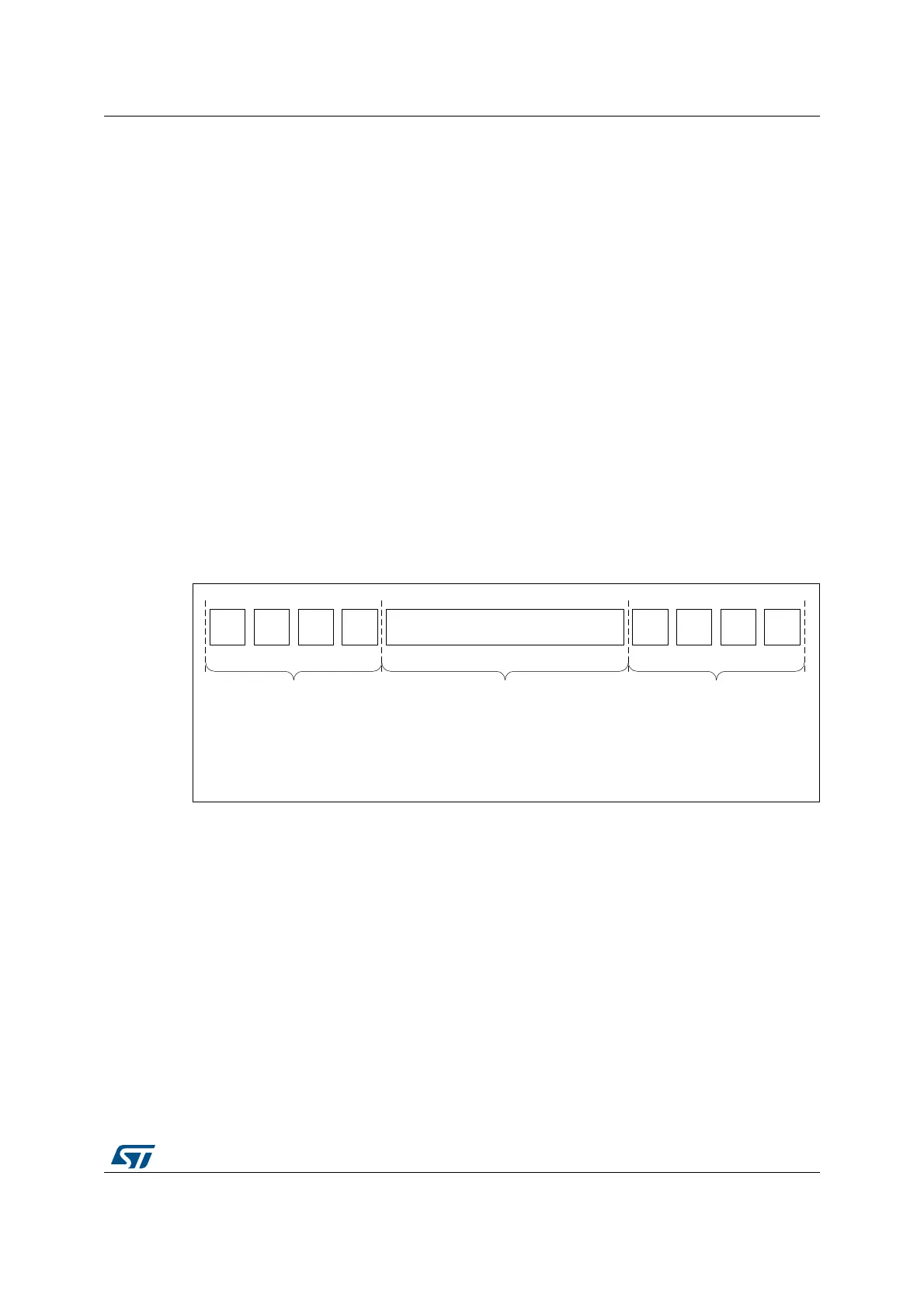

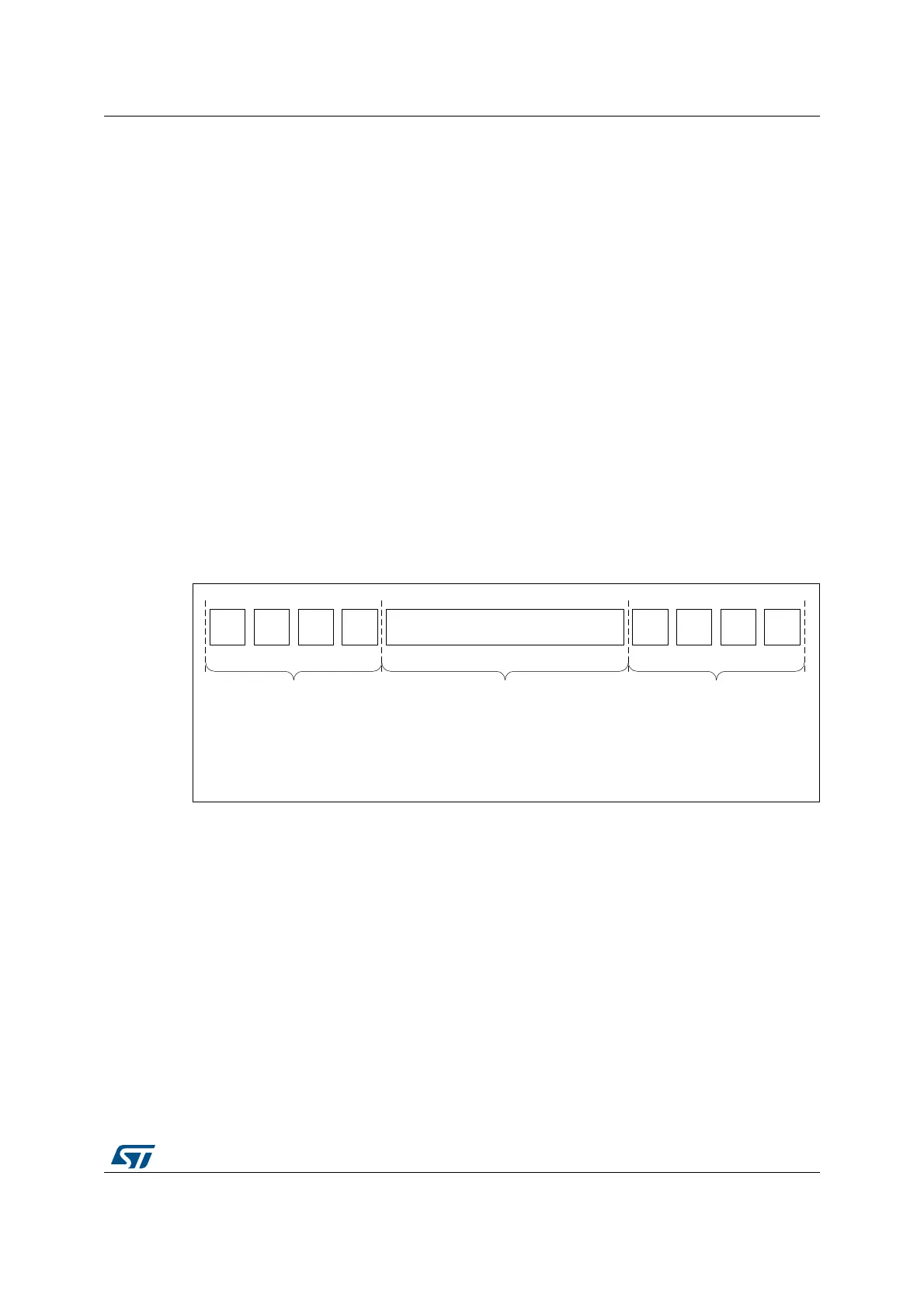

6. Write the AES_DINR register 4 times to input the cipher text (MSB first) as shown in

Figure 184: Mode 3: decryption with 128-bit key length.

7. Wait until the CCF flag is set in the AES_SR register.

8. Read the AES_DOUTR register 4 times to get the plain text (MSB first) as shown in

Figure 184: Mode 3: decryption with 128-bit key length.

9. Repeat steps 6, 7, 8 to process all the blocks using the same derivation key stored in

the AES_KEYRx registers.

Figure 184. Mode 3: decryption with 128-bit key length

25.9.4 Mode 4: key derivation and decryption

1. Disable the AES by resetting the EN bit in the AES_CR register.

2. Configure mode 4 by programming MODE[1:0] = 11 in the AES_CR register. This mode

is forbidden when AES is configured in CTR, GCM, GMAC or CMAC mode. It will be

069

:5

&7

:5

&7

:5

&7

:5

&7

:DLWXQWLOIODJ&&)

5'

37

5'

37

5'

37

5'

37

,QSXWSKDVH

ZULWHRSHUDWLRQVLQWR

$(6B',1>@

&RPSXWDWLRQSKDVH

2XWSXWSKDVH

UHDGRSHUDWLRQVRI

$(6B'287>@

37 SODLQWH[W ZRUGV37«37

&7 F\SKHUWH[W ZRUGV&7«&7

06% /6% 06% /6%

Loading...

Loading...