Independent watchdog (IWDG) RM0351

1054/1693 DocID024597 Rev 3

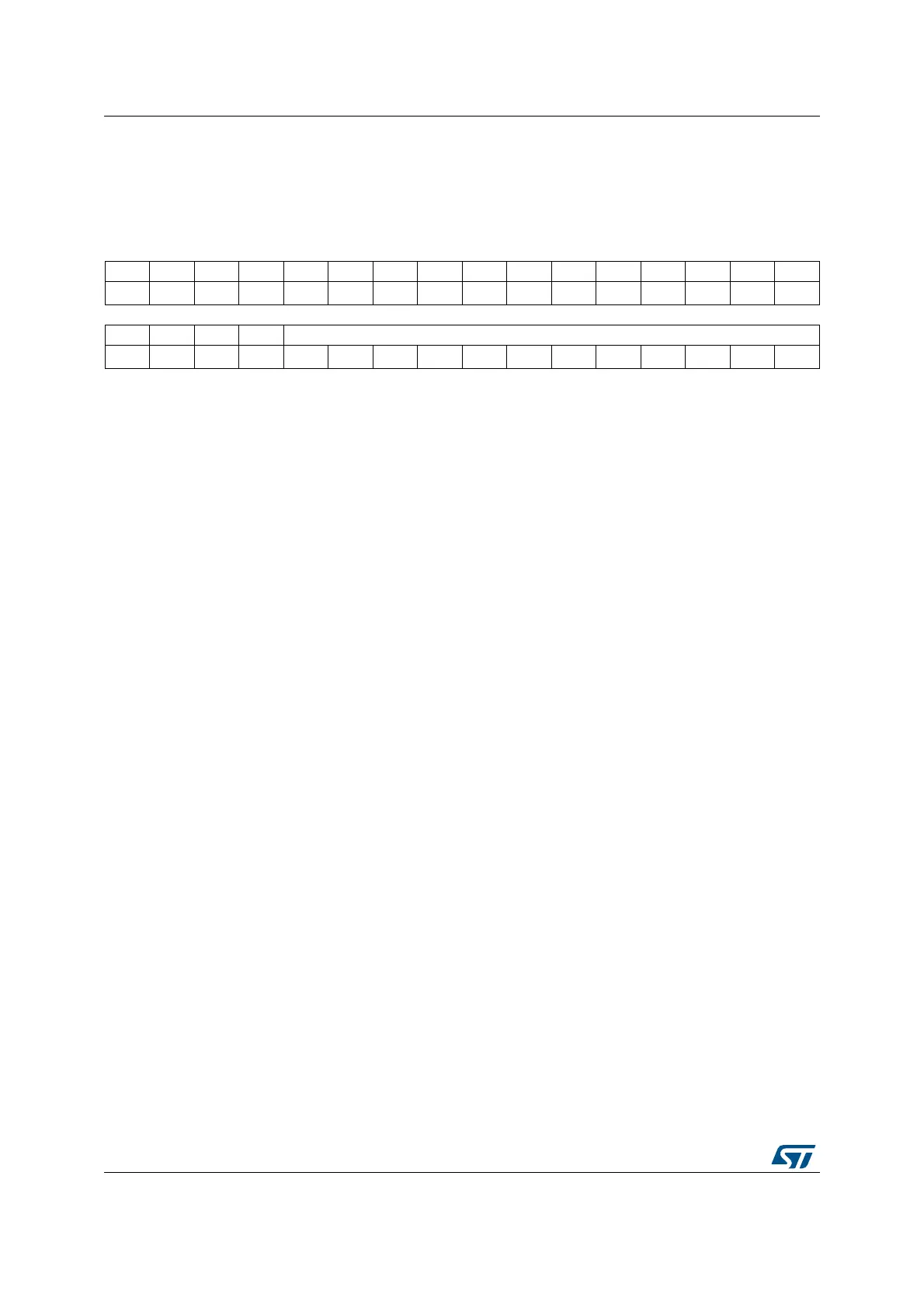

32.4.5 Window register (IWDG_WINR)

Address offset: 0x10

Reset value: 0x0000 0FFF (reset by Standby mode)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. WIN[11:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:12 Reserved, must be kept at reset value.

Bits11:0 WIN[11:0]: Watchdog counter window value

These bits are write access protected see Section 32.3.6. These bits contain the high limit of

the window value to be compared to the downcounter.

To prevent a reset, the downcounter must be reloaded when its value is lower than the

window register value and greater than 0x0

The WVU bit in the IWDG_SR register must be reset in order to be able to change the reload

value.

Note: Reading this register returns the reload value from the V

DD

voltage domain. This value

may not be valid if a write operation to this register is ongoing. For this reason the value

read from this register is valid only when the WVU bit in the IWDG_SR register is reset.

Loading...

Loading...