DocID024597 Rev 3 1141/1693

RM0351 Inter-integrated circuit (I2C) interface

1177

35.4.10 SMBus specific features

This section is relevant only when SMBus feature is supported. Please refer to Section 35.3:

I2C implementation.

Introduction

The System Management Bus (SMBus) is a two-wire interface through which various

devices can communicate with each other and with the rest of the system. It is based on I

2

C

principles of operation. SMBus provides a control bus for system and power management

related tasks.

This peripheral is compatible with the SMBUS specification rev 2.0 (http://smbus.org).

1. SCL period t

SCL

is greater than t

SCLL

+ t

SCLH

due to SCL internal detection delay. Values provided for t

SCL

are examples

only.

2. t

SYNC1 +

t

SYNC2

minimum value is 4 x t

I2CCLK

= 250 ns. Example with t

SYNC1 +

t

SYNC2

= 1000 ns

3. t

SYNC1 +

t

SYNC2

minimum value is 4 x t

I2CCLK

= 250 ns. Example with t

SYNC1 +

t

SYNC2

= 750 ns

4. t

SYNC1 +

t

SYNC2

minimum value is 4 x t

I2CCLK

= 250 ns. Example with t

SYNC1 +

t

SYNC2

= 500 ns

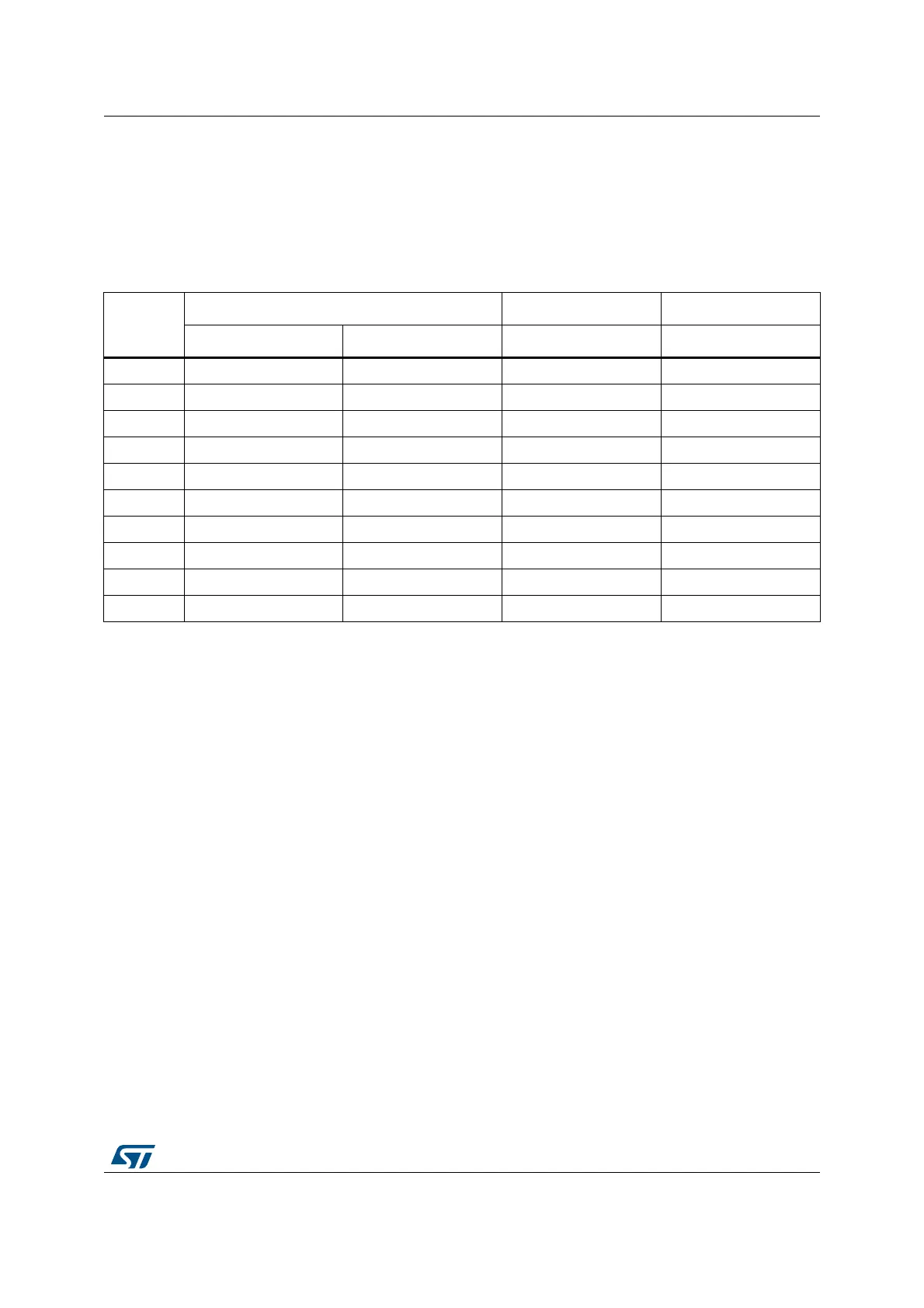

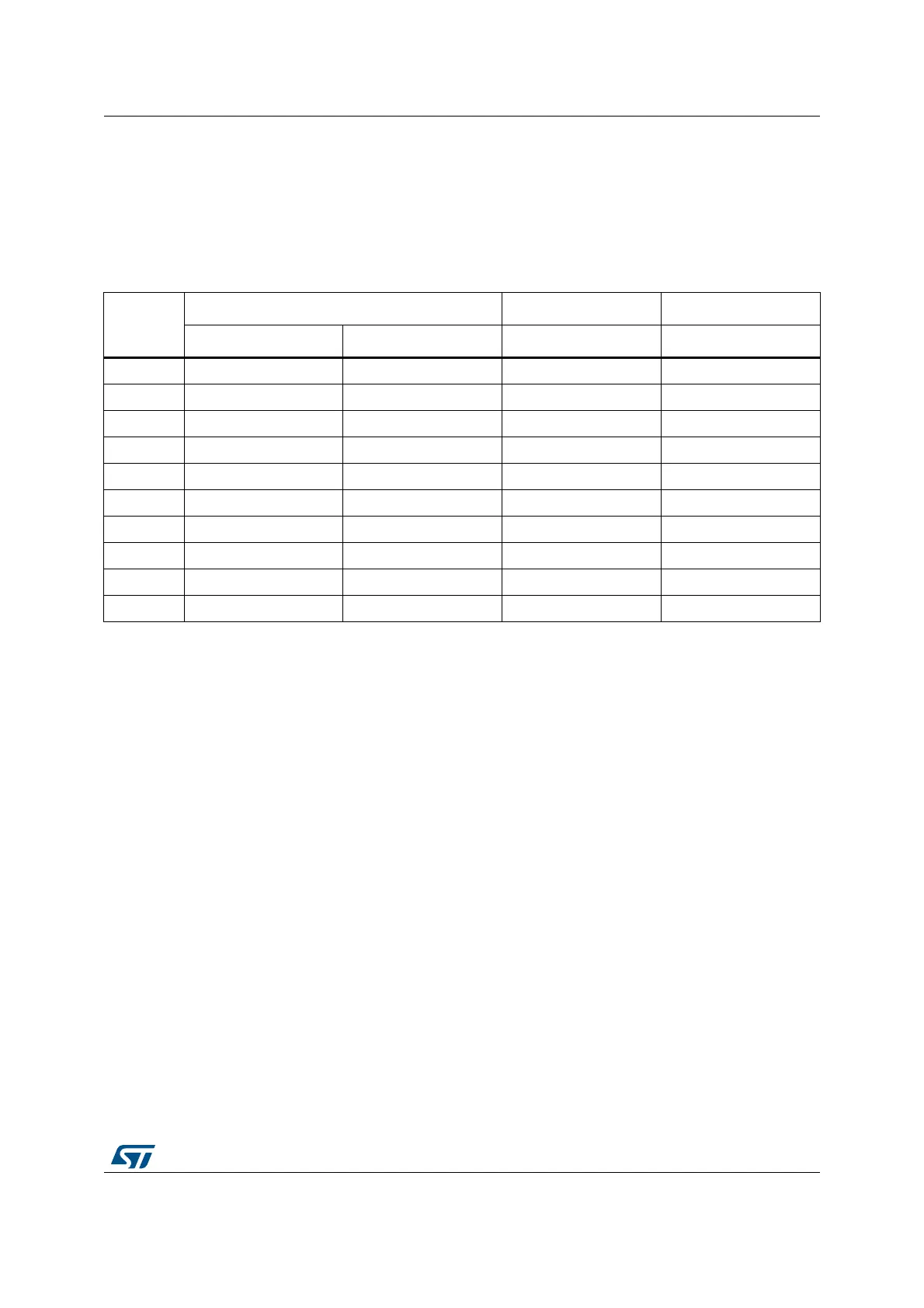

Table 182. Examples of timings settings for f

I2CCLK

= 48 MHz

Parameter

Standard-mode (Sm) Fast-mode (Fm) Fast-mode Plus (Fm+)

10 kHz 100 kHz 400 kHz 1000 kHz

PRESC 0xB 0xB 5 5

SCLL 0xC7 0x13 0x9 0x3

t

SCLL

200 x 250 ns = 50 µs 20 x 250 ns = 5.0 µs 10 x 125 ns = 1250 ns 4 x 125 ns = 500 ns

SCLH 0xC3 0xF 0x3 0x1

t

SCLH

196 x 250 ns = 49 µs 16 x 250 ns = 4.0 µs 4 x 125 ns = 500 ns 2 x 125 ns = 250 ns

t

SCL

(1)

~100 µs

(2)

~10 µs

(2)

~2500 ns

(3)

~875 ns

(4)

SDADEL 0x2 0x2 0x3 0x0

t

SDADEL

2 x 250 ns = 500 ns 2 x 250 ns = 500 ns 3 x 125 ns = 375 ns 0 ns

SCLDEL 0x4 0x4 0x3 0x1

t

SCLDEL

5 x 250 ns = 1250 ns 5 x 250 ns = 1250 ns 4 x 125 ns = 500 ns 2 x 125 ns = 250 ns

1. The SCL period t

SCL

is greater than t

SCLL

+ t

SCLH

due to the SCL internal detection delay. Values provided for t

SCL

are only

examples.

2. t

SYNC1 +

t

SYNC2

minimum value is 4x t

I2CCLK

= 83.3 ns. Example with t

SYNC1 +

t

SYNC2

= 1000 ns

3. t

SYNC1 +

t

SYNC2

minimum value is 4x t

I2CCLK

= 83.3 ns. Example with t

SYNC1 +

t

SYNC2

= 750 ns

4. t

SYNC1 +

t

SYNC2

minimum value is 4x t

I2CCLK

= 83.3 ns. Example with t

SYNC1 +

t

SYNC2

= 250 ns

Loading...

Loading...