Reset and clock control (RCC) RM0351

218/1693 DocID024597 Rev 3

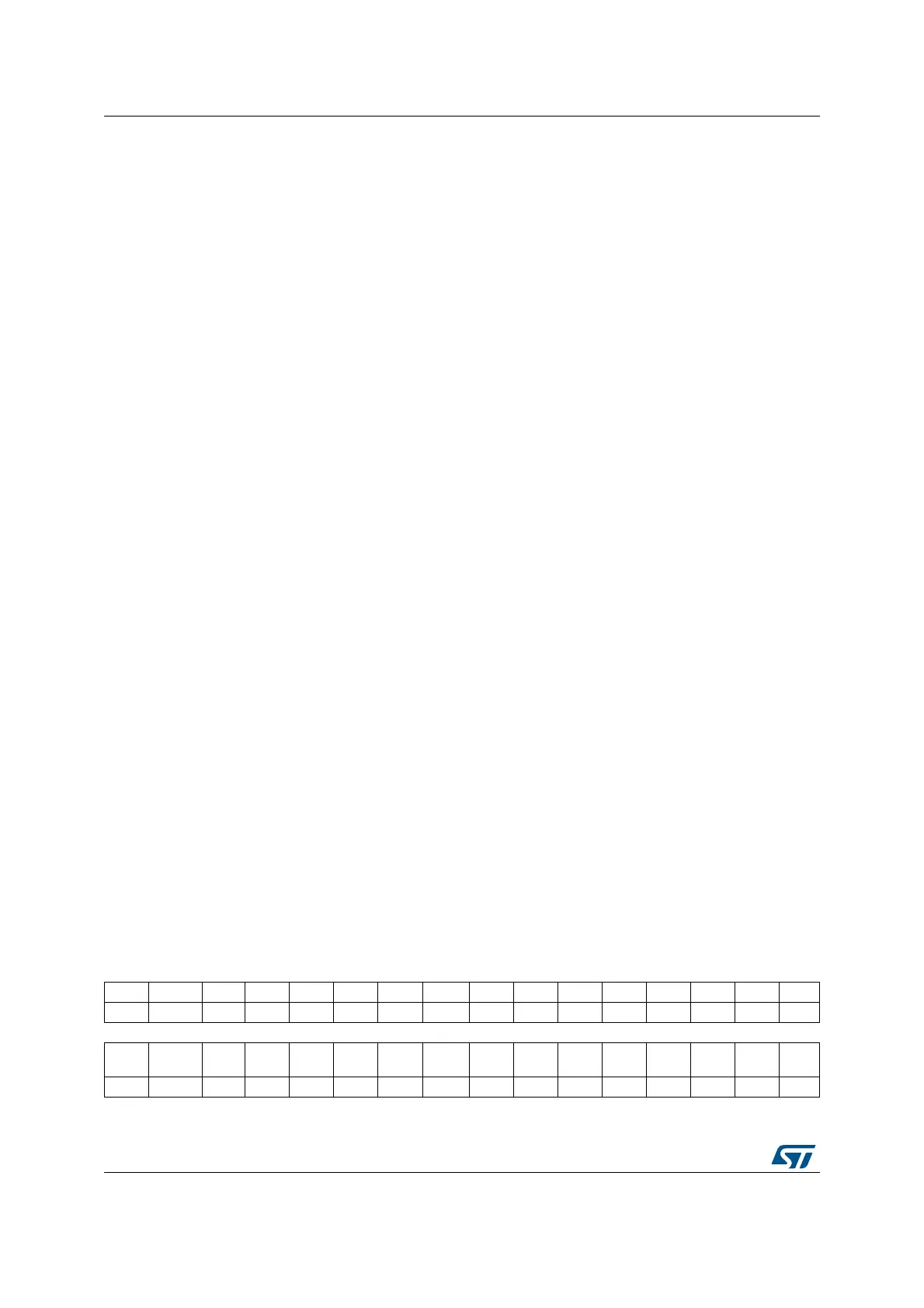

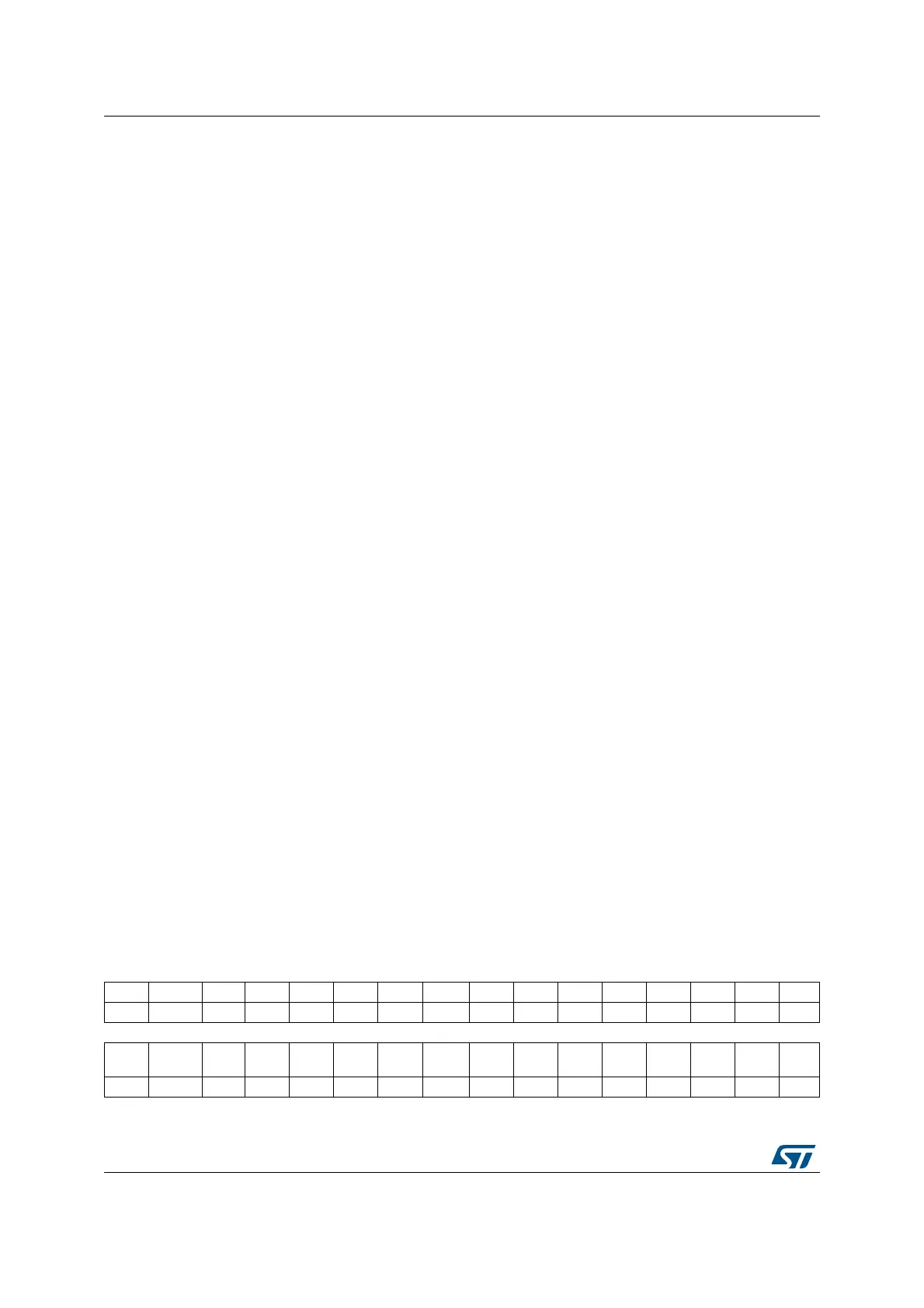

6.4.12 AHB3 peripheral reset register (RCC_AHB3RSTR)

Address offset: 0x30

Reset value: 0x00000 0000

Access: no wait state, word, half-word and byte access

Bit 7 GPIOHRST: IO port H reset

Set and cleared by software.

0: No effect

1: Reset IO port H

Bit 6 GPIOGRST: IO port G reset

Set and cleared by software.

0: No effect

1: Reset IO port G

Bit 5 GPIOFRST: IO port F reset

Set and cleared by software.

0: No effect

1: Reset IO port F

Bit 4 GPIOERST: IO port E reset

Set and cleared by software.

0: No effect

1: Reset IO port E

Bit 3 GPIODRST: IO port D reset

Set and cleared by software.

0: No effect

1: Reset IO port D

Bit 2 GPIOCRST: IO port C reset

Set and cleared by software.

0: No effect

1: Reset IO port C

Bit 1 GPIOBRST: IO port B reset

Set and cleared by software.

0: No effect

1: Reset IO port B

Bit 0 GPIOARST: IO port A reset

Set and cleared by software.

0: No effect

1: Reset IO port A

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 76543210

Res. Res. Res. Res. Res. Res. Res.

QSPI

RST

Res. Res. Res. Res. Res. Res. Res.

FMC

RST

rw rw

Loading...

Loading...