Quad-SPI interface (QUADSPI) RM0351

400/1693 DocID024597 Rev 3

15 Quad-SPI interface (QUADSPI)

15.1 Introduction

The QUADSPI is a specialized communication interface targeting single, dual or quad SPI

Flash memories. It can operate in any of the three following modes:

• indirect mode: all the operations are performed using the QUADSPI registers

• status polling mode: the external Flash memory status register is periodically read and

an interrupt can be generated in case of flag setting

• memory-mapped mode: the external Flash memory is mapped to the microcontroller

address space and is seen by the system as if it was an internal memory

15.2 QUADSPI main features

• Three functional modes: indirect, status-polling, and memory-mapped

• SDR and DDR support

• Fully programmable opcode for both indirect and memory mapped mode

• Fully programmable frame format for both indirect and memory mapped mode

• Integrated FIFO for reception and transmission

• 8, 16, and 32-bit data accesses are allowed

• DMA channel for indirect mode operations

• Interrupt generation on FIFO threshold, timeout, operation complete, and access error

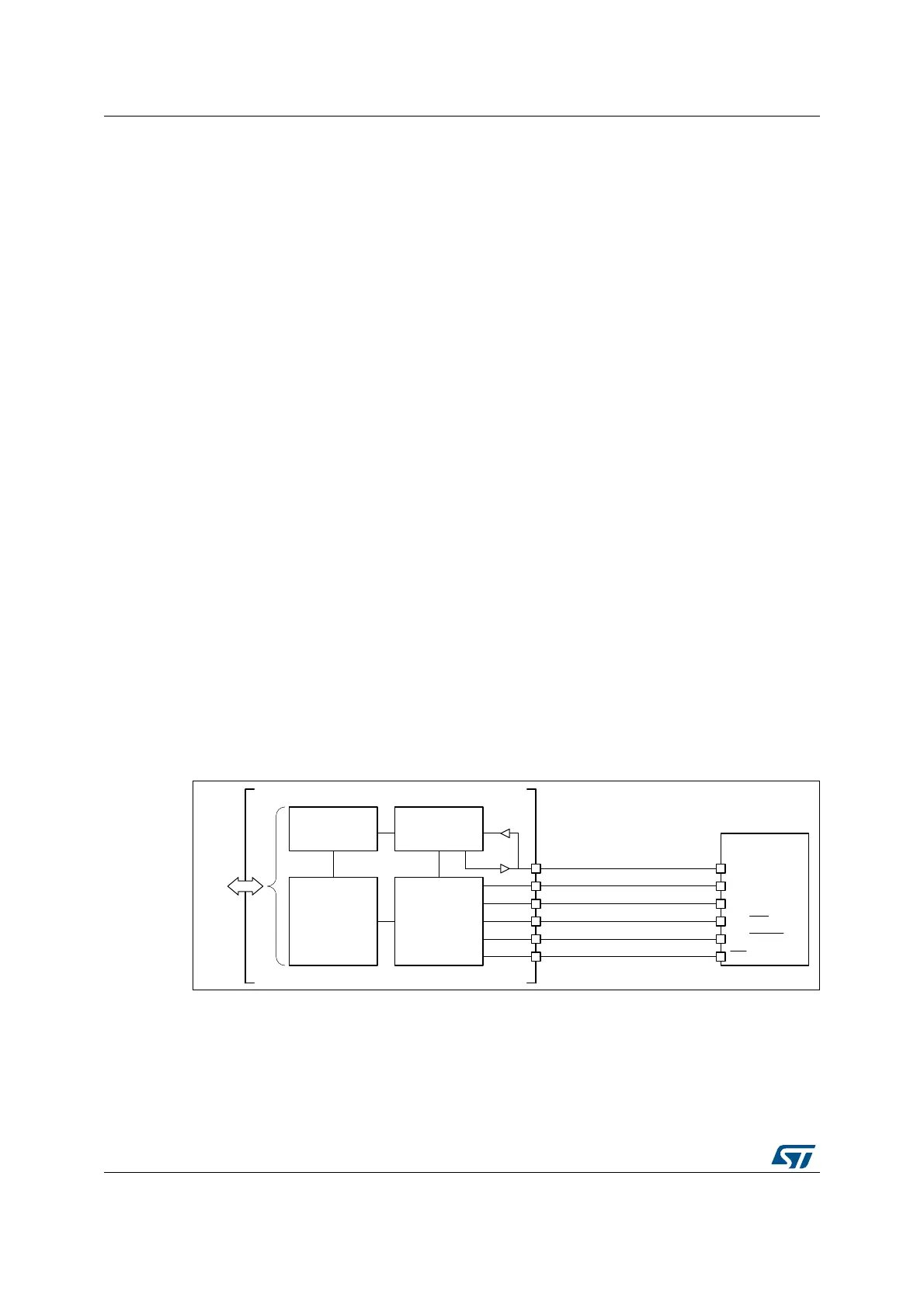

15.3 QUADSPI functional description

15.3.1 QUADSPI block diagram

Figure 51. QUADSPI block diagram

63,)/$6+

069

&/.

%.B,262

%.B,26,

%.B,2

%.B,2

&/.

46,

462

4:3

4+2/'

%.BQ&6

&6

$+%

5HJLVWHUV

FRQWURO

&ORFN

PDQDJHPHQW

),)2 6KLIWUHJLVWHU

48$'63,

Loading...

Loading...