Quad-SPI interface (QUADSPI) RM0351

416/1693 DocID024597 Rev 3

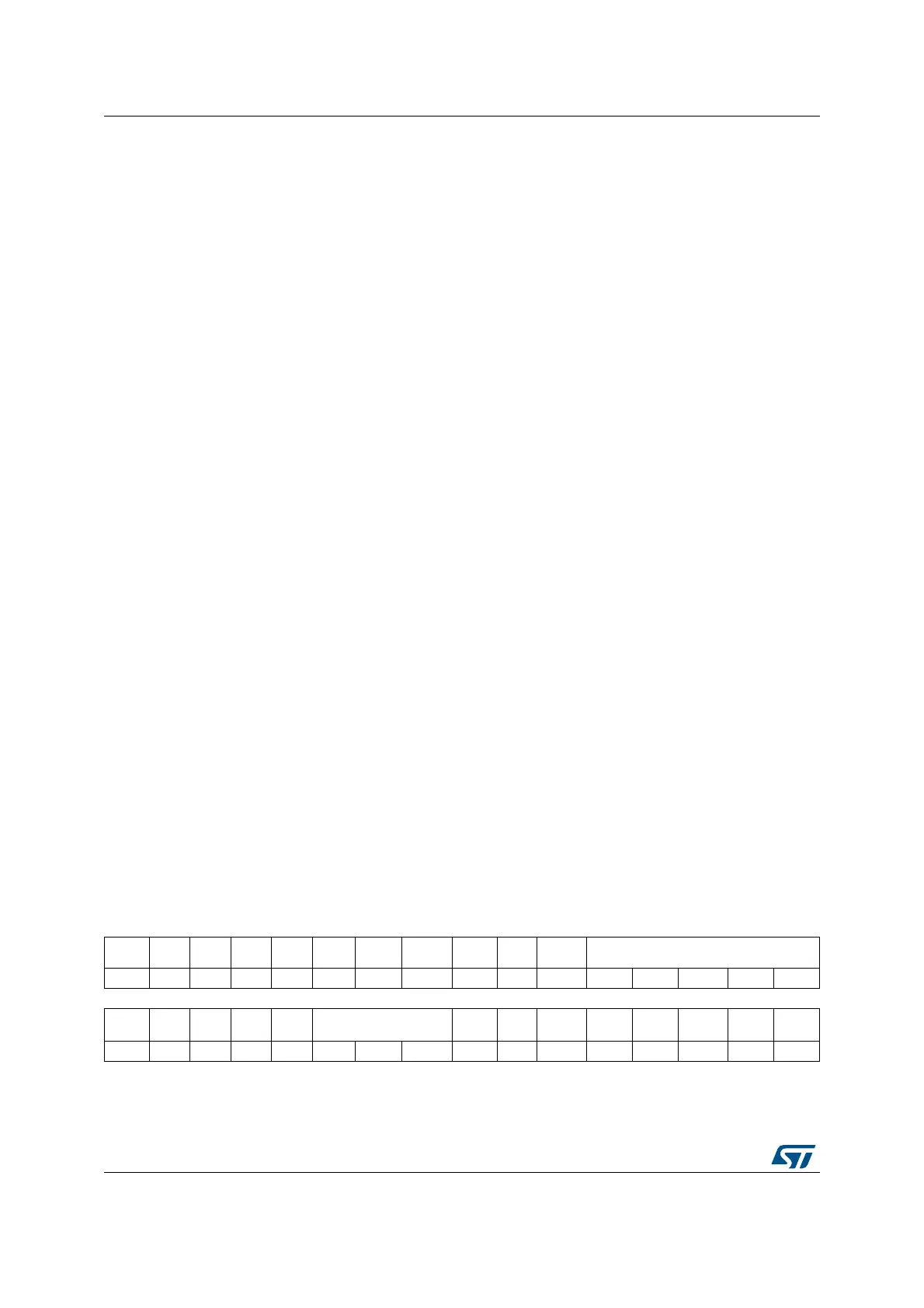

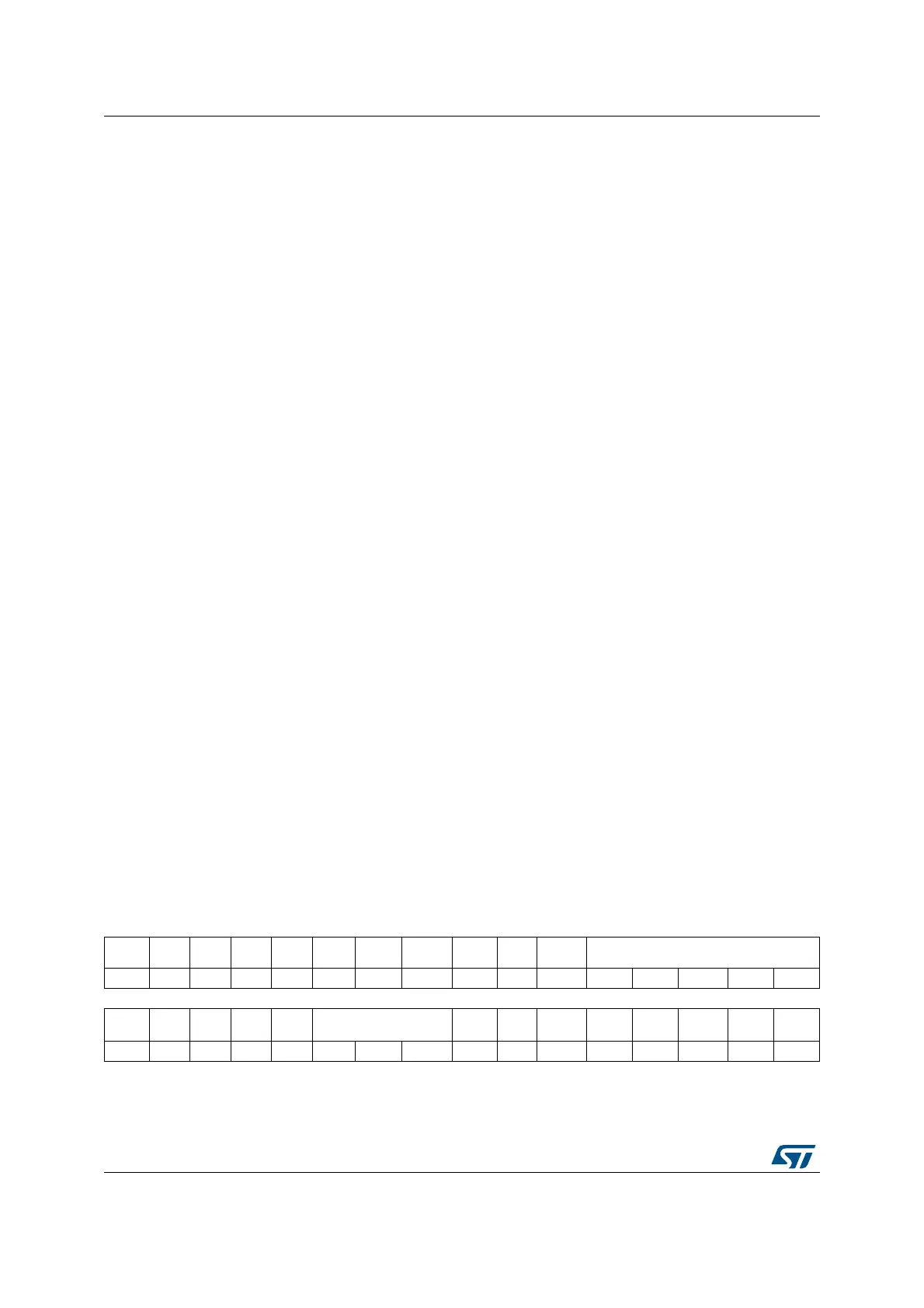

15.5.2 QUADSPI device configuration register (QUADSPI_DCR)

Address offset: 0x0004

Reset value: 0x0000 0000

Bit 3 TCEN: Timeout counter enable

This bit is valid only when memory-mapped mode (FMODE = 11) is selected. Activating

this bit causes the chip select (nCS) to be released (and thus reduces consumption) if

there has not been an access after a certain amount of time, where this time is defined

by TIMEOUT[15:0] (QUADSPI_LPTR).

Enable the timeout counter.

By default, the QUADSPI never stops its prefetch operation, keeping the previous read

operation active with nCS maintained low, even if no access to the Flash memory

occurs for a long time. Since Flash memories tend to consume more when nCS is held

low, the application might want to activate the timeout counter (TCEN = 1,

QUADSPI_CR[3]) so that nCS is released after a period of TIMEOUT[15:0]

(QUADSPI_LPTR) cycles have elapsed without an access since when the FIFO

becomes full with prefetch data.

0: Timeout counter is disabled, and thus the chip select (nCS) remains active

indefinitely after an access in memory-mapped mode.

1: Timeout counter is enabled, and thus the chip select is released in memory-mapped

mode after TIMEOUT[15:0] cycles of Flash memory inactivity.

This bit can be modified only when BUSY = 0.

Bit 2 DMAEN: DMA enable

In indirect mode, DMA can be used to input or output data via the QUADSPI_DR

register. DMA transfers are initiated when the FIFO threshold flag, FTF, is set.

0: DMA is disabled for indirect mode

1: DMA is enabled for indirect mode

Bit 1 ABORT: Abort request

This bit aborts the on-going command sequence. It is automatically reset once the abort

is complete.

This bit stops the current transfer.

In polling mode or memory-mapped mode, this bit also reset the APM bit or the DM bit.

0: No abort requested

1: Abort requested

Bit 0 EN: Enable

Enable the QUADSPI.

0: QUADSPI is disabled

1: QUADSPI is enabled

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. FSIZE

rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. CSHT Res. Res. Res. Res. Res. Res. Res.

CK-

MODE

rw rw rw rw

Loading...

Loading...