DocID024597 Rev 3 71/1693

RM0351

77

2.3 Bit banding

The Cortex

®

-M4 memory map includes two bit-band regions. These regions map each word

in an alias region of memory to a bit in a bit-band region of memory. Writing to a word in the

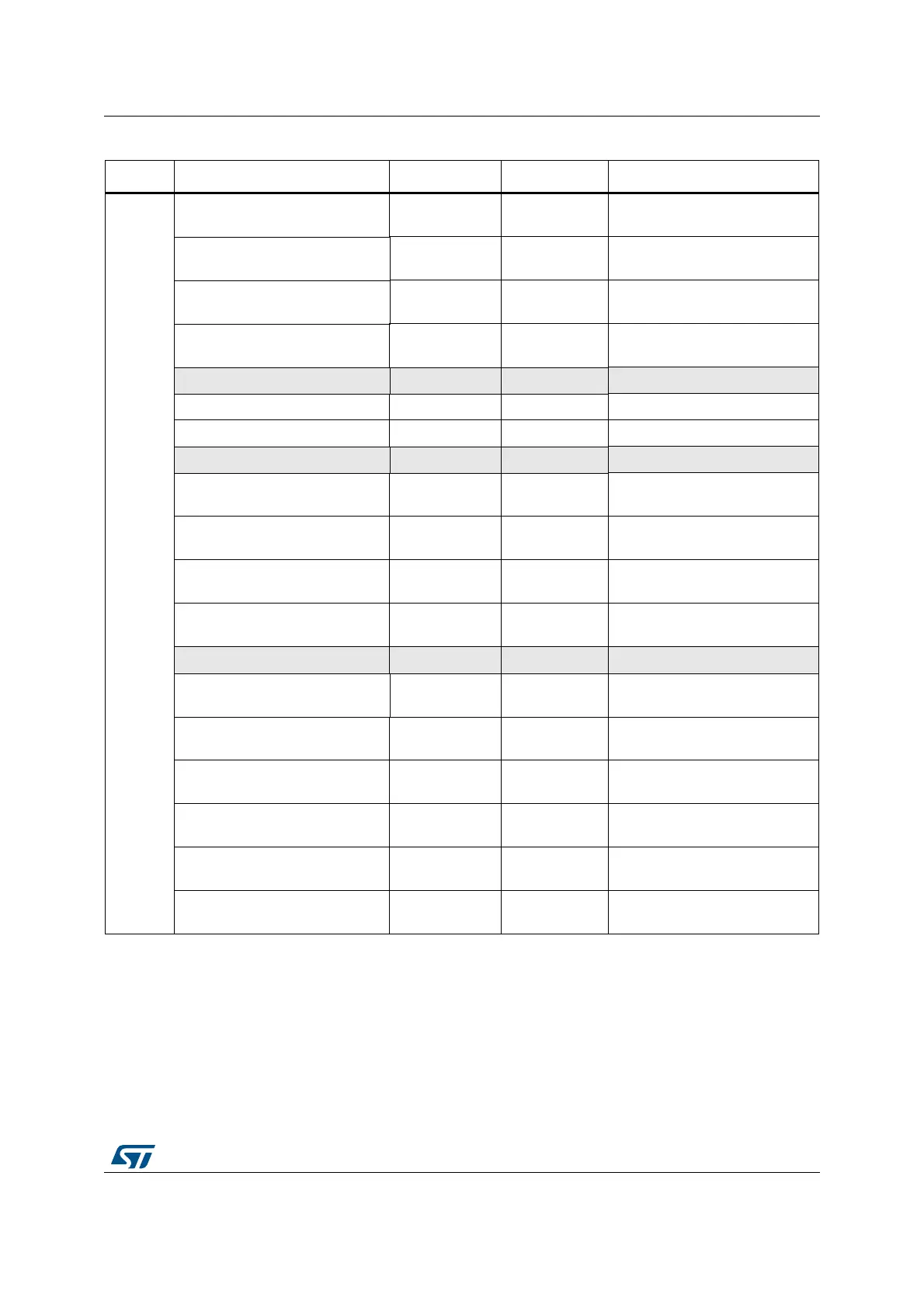

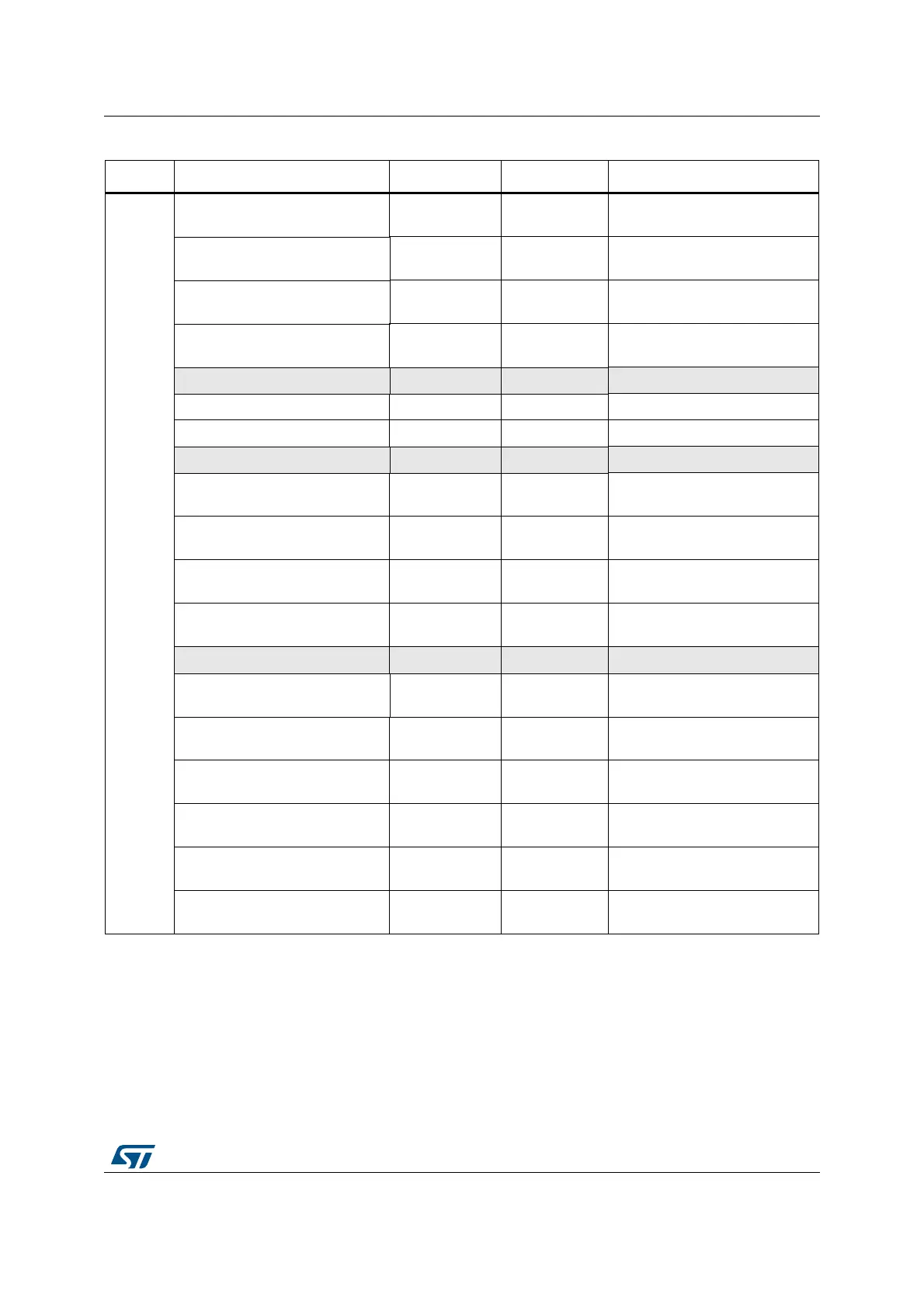

APB1

0x4000 5000 - 0x4000 53FF 1 KB UART5

Section 36.8.12: USART

register map

0x4000 4C00 - 0x4000 4FFF 1 KB UART4

Section 36.8.12: USART

register map

0x4000 4800 - 0x4000 4BFF 1 KB USART3

Section 36.8.12: USART

register map

0x4000 4400 - 0x4000 47FF 1 KB USART2

Section 36.8.12: USART

register map

0x4000 4000 - 0x4000 43FF 1KB Reserved -

0x4000 3C00 - 0x4000 3FFF 1 KB SPI3 Section 38.6.8: SPI register map

0x4000 3800 - 0x4000 3BFF 1 KB SPI2 Section 38.6.8: SPI register map

0x4000 3400 - 0x4000 37FF 1KB Reserved -

0x4000 3000 - 0x4000 33FF 1 KB IWDG

Section 32.4.6: IWDG register

map

0x4000 2C00 - 0x4000 2FFF 1 KB WWDG

Section 33.4.4: WWDG register

map

0x4000 2800 - 0x4000 2BFF 1 KB RTC

Section 34.6.21: RTC register

map

0x4000 2400 - 0x4000 27FF 1 KB LCD

Section 22.6.6: LCD register

map

0x4000 1800 - 0x4000 2400 3KB Reserved -

0x4000 1400 - 0x4000 17FF 1 KB TIM7

Section 29.4.9: TIM6/TIM7

register map

0x4000 1000 - 0x4000 13FF 1 KB TIM6

Section 29.4.9: TIM6/TIM7

register map

0x4000 0C00- 0x4000 0FFF 1 KB TIM5

Section 27.4.23: TIMx register

map

0x4000 0800 - 0x4000 0BFF 1 KB TIM4

Section 27.4.23: TIMx register

map

0x4000 0400 - 0x4000 07FF 1 KB TIM3

Section 27.4.23: TIMx register

map

0x4000 0000 - 0x4000 03FF 1 KB TIM2

Section 27.4.23: TIMx register

map

Table 1. STM32L4x6 memory map and peripheral register boundary addresses (continued)

Bus Boundary address Size (bytes) Peripheral Peripheral register map

Loading...

Loading...