DocID024597 Rev 3 1117/1693

RM0351 Inter-integrated circuit (I2C) interface

1177

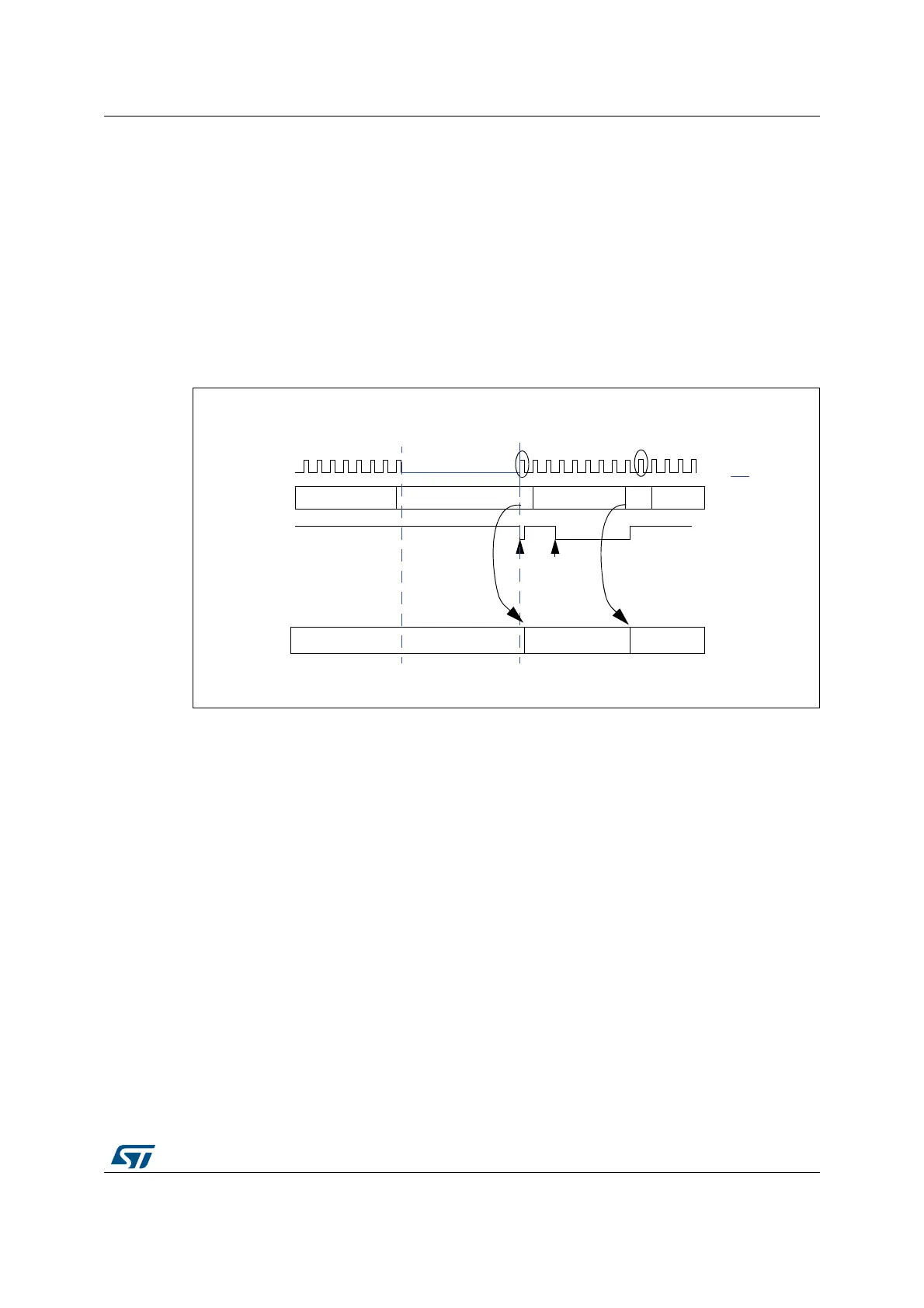

35.4.6 Data transfer

The data transfer is managed through transmit and receive data registers and a shift

register.

Reception

The SDA input fills the shift register. After the 8th SCL pulse (when the complete data byte is

received), the shift register is copied into I2C_RXDR register if it is empty (RXNE=0). If

RXNE=1, meaning that the previous received data byte has not yet been read, the SCL line

is stretched low until I2C_RXDR is read. The stretch is inserted between the 8th and 9th

SCL pulse (before the Acknowledge pulse).

Figure 356. Data reception

XX

3HIFTREGISTER

DATA

DATA

XX DATA

28.%

!#+PULSE

DATA DATA

!#+PULSE

XX

)#?28$2

RDDATARDDATA

3#,

LEGEND

3#,

STRETCH

-36

Loading...

Loading...