DocID024597 Rev 3 1129/1693

RM0351 Inter-integrated circuit (I2C) interface

1177

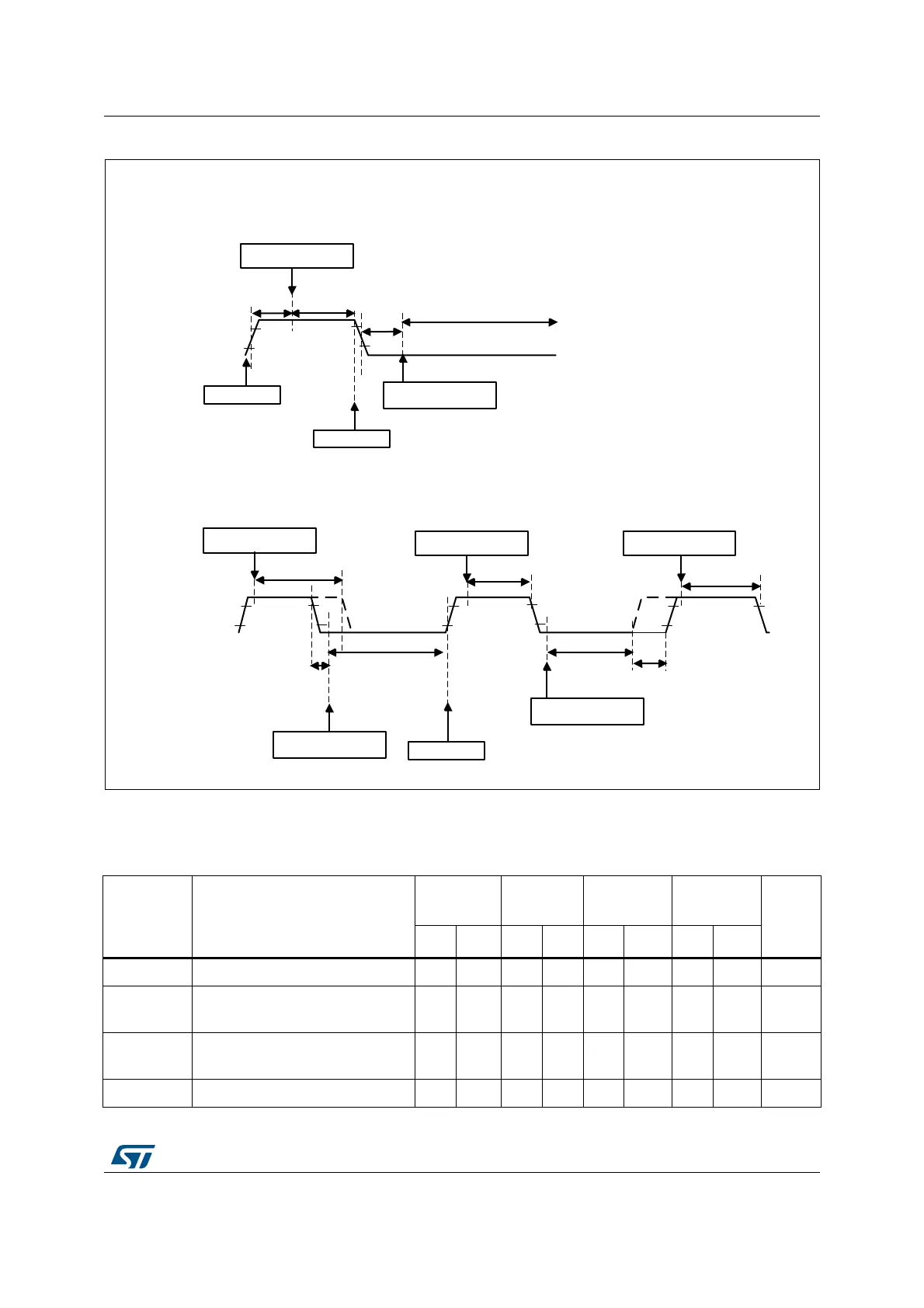

Figure 365. Master clock generation

Caution: In order to be I

2

C or SMBus compliant, the master clock must respect the timings given

below:

069

W

6<1&

6&/KLJKOHYHOGHWHFWHG

6&/+FRXQWHUVWDUWV

6&/+

6&/

6&/PDVWHUFORFNJHQHUDWLRQ

6&/UHOHDVHG

6&/ORZOHYHOGHWHFWHG

6&//FRXQWHUVWDUWV

6&/GULYHQORZ

6&//

W

6<1&

6&/PDVWHUFORFNV\QFKURQL]DWLRQ

6&//

6&/GULYHQORZE\

DQRWKHUGHYLFH

6&/ORZOHYHOGHWHFWHG

6&//FRXQWHUVWDUWV

6&/UHOHDVHG

6&/+

6&/+

6&/KLJKOHYHOGHWHFWHG

6&/+FRXQWHUVWDUWV

6&/KLJKOHYHOGHWHFWHG

6&/+FRXQWHUVWDUWV

6&/ORZOHYHOGHWHFWHG

6&//FRXQWHUVWDUWV

6&//

6&/GULYHQORZE\

DQRWKHUGHYLFH

6&/+

6&/KLJKOHYHOGHWHFWHG

6&/+FRXQWHUVWDUWV

Table 179. I

2

C-SMBUS specification clock timings

Symbol Parameter

Standard-

mode (Sm)

Fast-mode

(Fm)

Fast-mode

Plus (Fm+)

SMBUS

Unit

Min Max Min Max Min Max Min Max

f

SCL

SCL clock frequency

100 400 1000 100 kHz

t

HD:STA

Hold time (repeated) START

condition

4.0 - 0.6 0.26 - 4.0 - µs

t

SU:STA

Set-up time for a repeated

START condition

4.7 - 0.6 0.26 - 4.7 - µs

t

SU:STO

Set-up time for STOP condition

4.0 - 0.6 0.26 - 4.0 - µs

Loading...

Loading...