DocID024597 Rev 3 743/1693

RM0351 Advanced encryption standard hardware accelerator (AES)

751

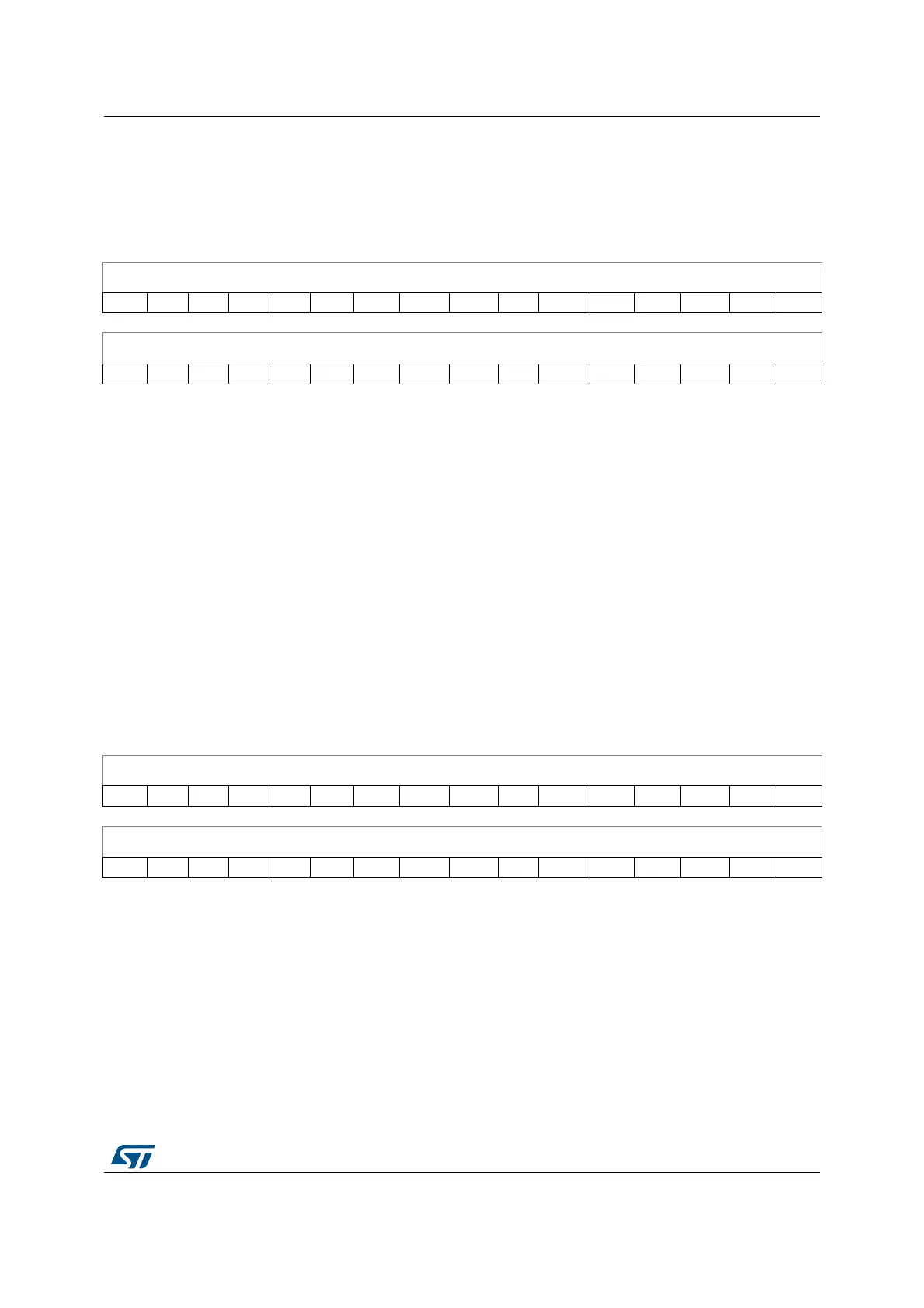

25.14.5 AES key register 0 (AES_KEYR0) (LSB: key [31:0])

Address offset: 0x10

Reset value: 0x0000 0000

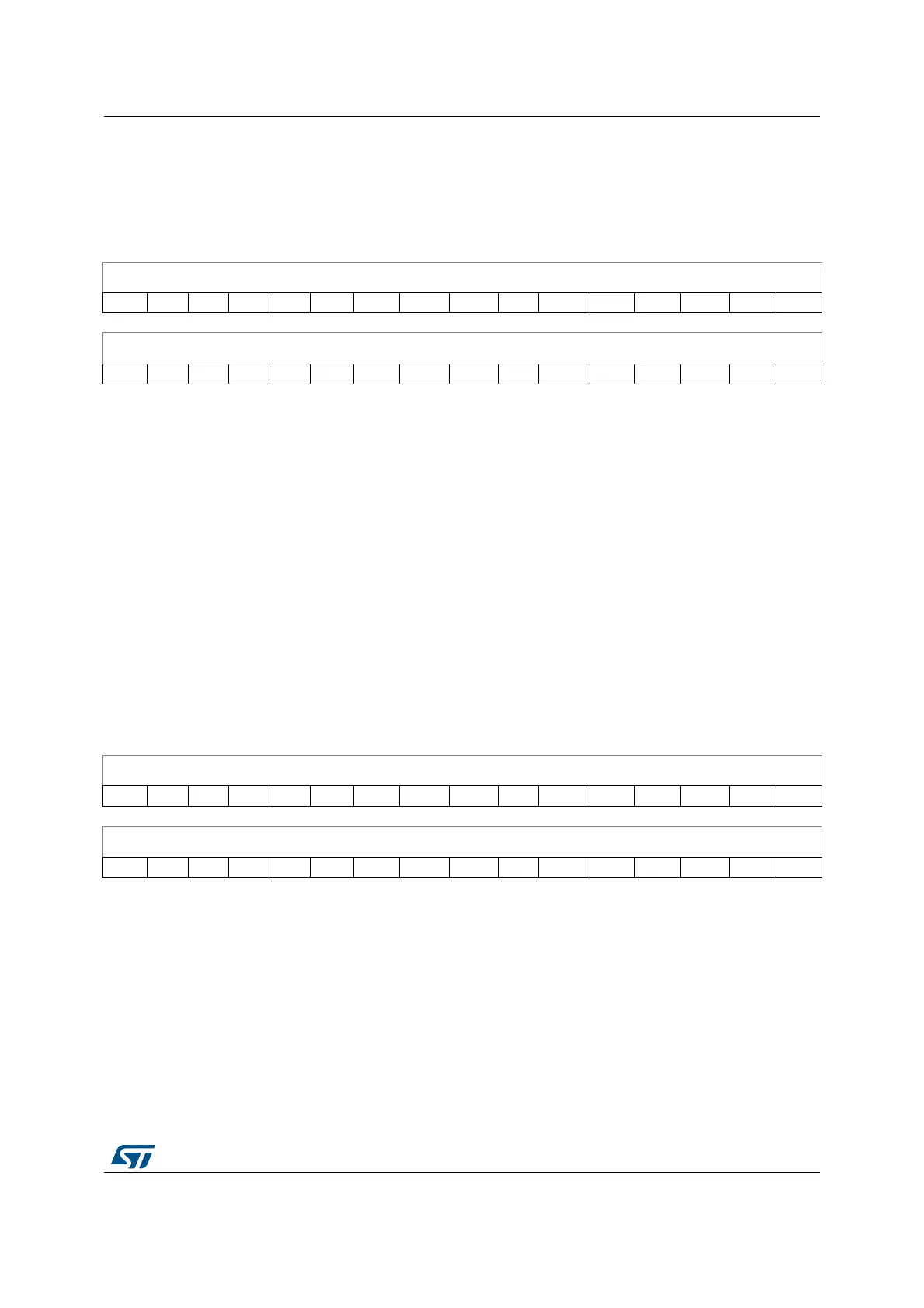

25.14.6 AES key register 1 (AES_KEYR1) (key[63:32])

Address offset: 0x14

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

KEYR0[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

KEYR0[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 KEYR0[31:0]: Data output register (LSB key [31:0])

This register must be written before the EN bit in the AES_CR register is set:

In mode 1 (encryption), mode 2 (key derivation) and mode 4 (key derivation + decryption), the value to

be written represents the encryption key from LSB, meaning key [31:0].

In mode 3 (decryption), the value to be written represents the decryption key from LSB, meaning key

[31:0]. When the register is written with the encryption key in this decryption mode, reading it before

the AES is enabled will return the encryption value. Reading it after CCF flag is set will return the

derivation key.

Reading this register while AES is enabled returns an unpredictable value.

Note: This register does not contain the derivation key in mode 4 (derivation key + decryption). It

always contains the encryption key value.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

KEYR1[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

KEYR1[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 KEYR1[31:0]: Data output register (key [63:32])

Refer to the description of AES_KEYR0.

Loading...

Loading...