DocID024597 Rev 3 713/1693

RM0351 Random number generator (RNG)

714

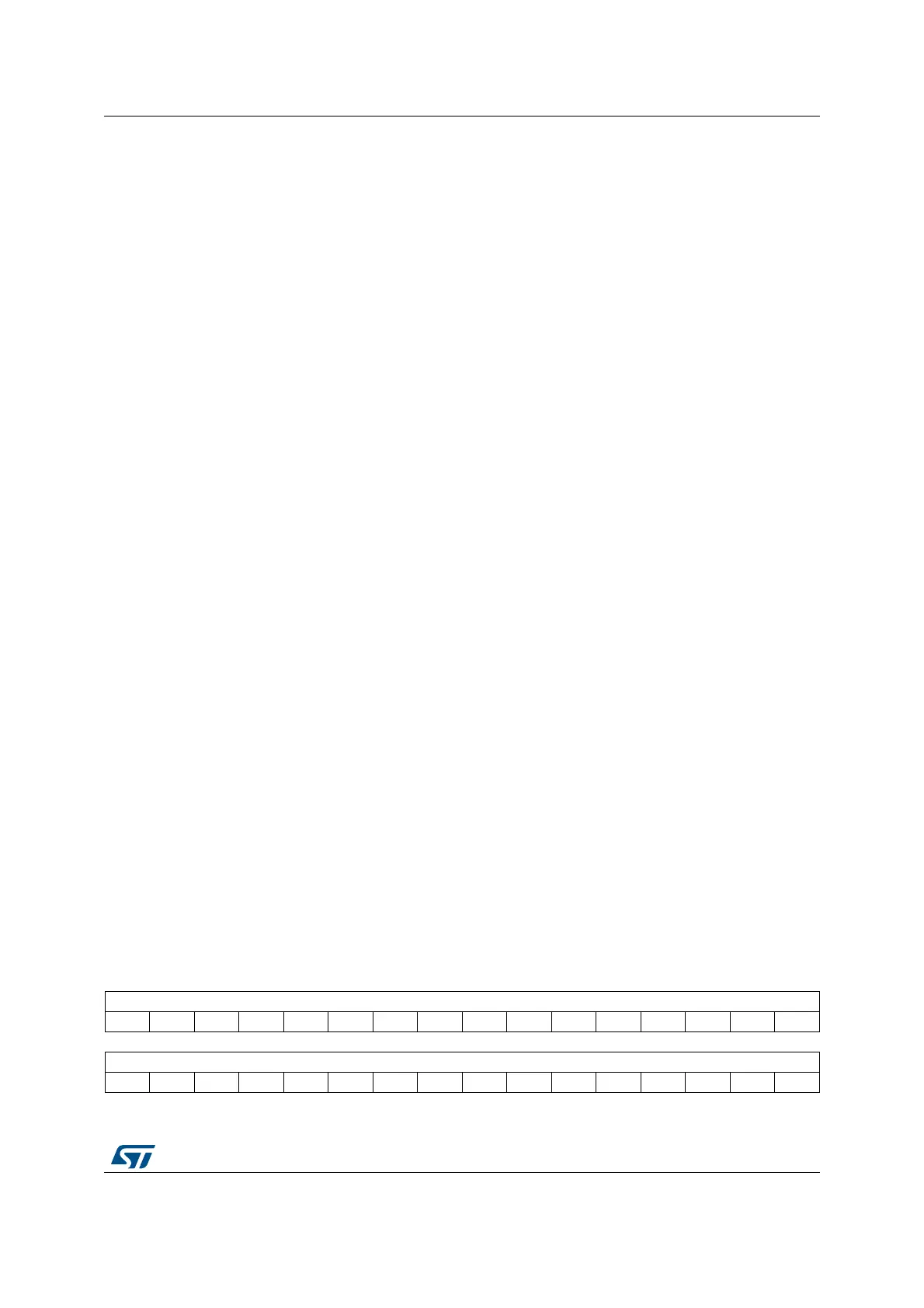

24.4.3 RNG data register (RNG_DR)

Address offset: 0x08

Reset value: 0x0000 0000

The RNG_DR register is a read-only register that delivers a 32-bit random value when read.

After being read, this register delivers a new random value after a maximum time of 40

periods of the RNG_CLK clock. The software must check that the DRDY bit is set before

reading the RNDATA value.

Bits 31:7 Reserved, must be kept at reset value

Bit 6 SEIS: Seed error interrupt status

This bit is set at the same time as SECS, it is cleared by writing it to 0.

0: No faulty sequence detected

1: One of the following faulty sequences has been detected:

– More than 64 consecutive bits at the same value (0 or 1)

– More than 32 consecutive alternations of 0 and 1 (0101010101...01)

An interrupt is pending if IE = 1 in the RNG_CR register.

Bit 5 CEIS: Clock error interrupt status

This bit is set at the same time as CECS, it is cleared by writing it to 0.

0: The RNG_CLK clock was correctly detected

1: The RNG_CLK was not correctly detected (f

RNG_CLK

< f

HCLK

/16)

An interrupt is pending if IE = 1 in the RNG_CR register.

Bits 4:3 Reserved, must be kept at reset value

Bit 2 SECS: Seed error current status

0: No faulty sequence has currently been detected. If the SEIS bit is set, this means that a

faulty sequence was detected and the situation has been recovered.

1: One of the following faulty sequences has been detected:

– More than 64 consecutive bits at the same value (0 or 1)

– More than 32 consecutive alternations of 0 and 1 (0101010101...01)

Bit 1 CECS: Clock error current status

0: The RNG_CLK clock has been correctly detected. If the CEIS bit is set, this means that a

clock error was detected and the situation has been recovered

1: The RNG_CLK was not correctly detected (f

RNG_CLK

< f

HCLK

/16).

Bit 0 DRDY: Data ready

0: The RNG_DR register is not yet valid, no random data is available

1: The RNG_DR register contains valid random data

Note: An interrupt is pending if IE = 1 in the RNG_CR register.

Once the RNG_DR register has been read, this bit returns to 0 until a new valid value is

computed.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RNDATA

rrrrrrrrrrrrrrrr

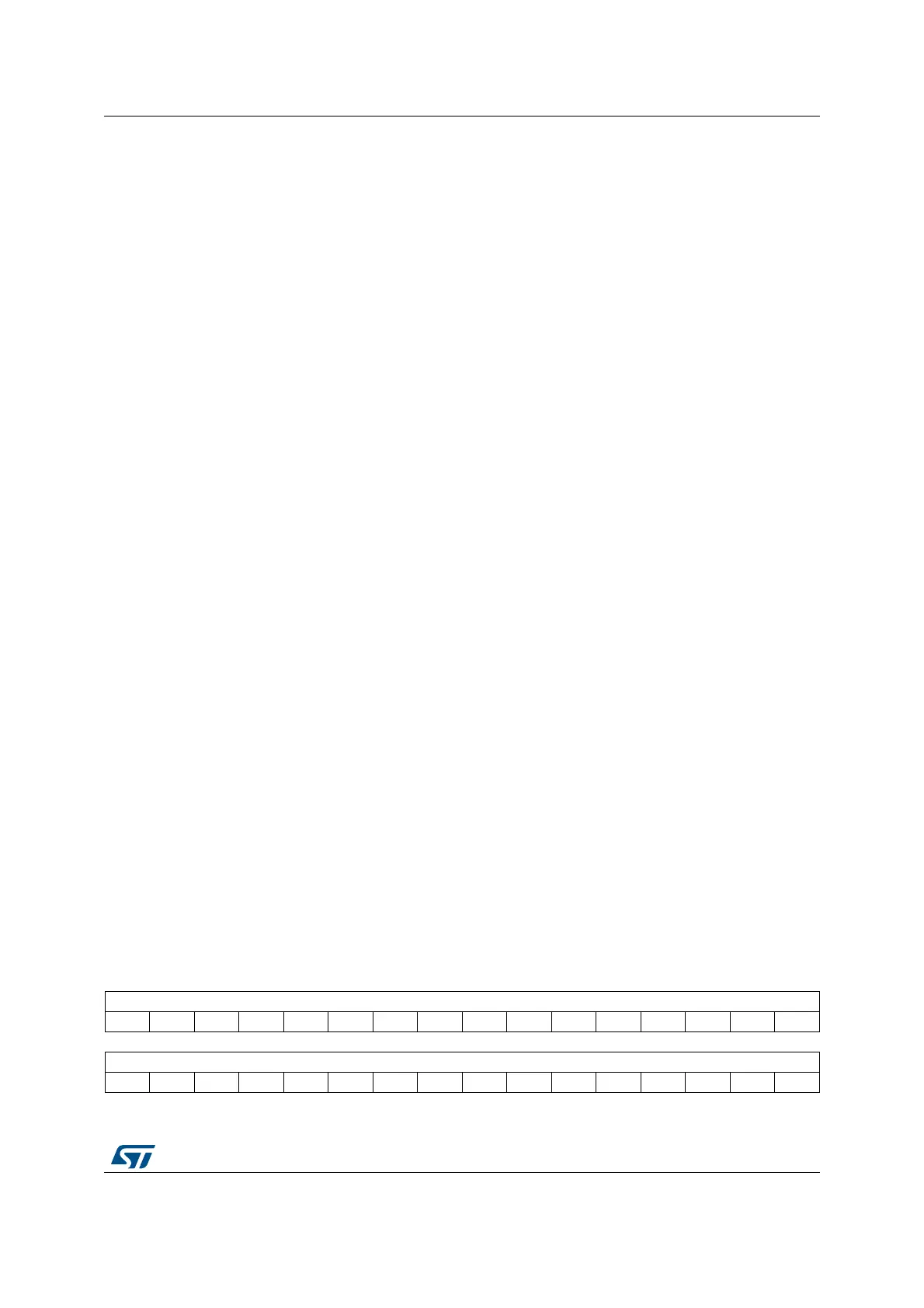

1514131211109876543210

RNDATA

rrrrrrrrrrrrrrrr

Loading...

Loading...