DocID024597 Rev 3 1113/1693

RM0351 Inter-integrated circuit (I2C) interface

1177

I2C timings

The timings must be configured in order to guarantee a correct data hold and setup time,

used in master and slave modes. This is done by programming the PRESC[3:0],

SCLDEL[3:0] and SDADEL[3:0] bits in the I2C_TIMINGR register.

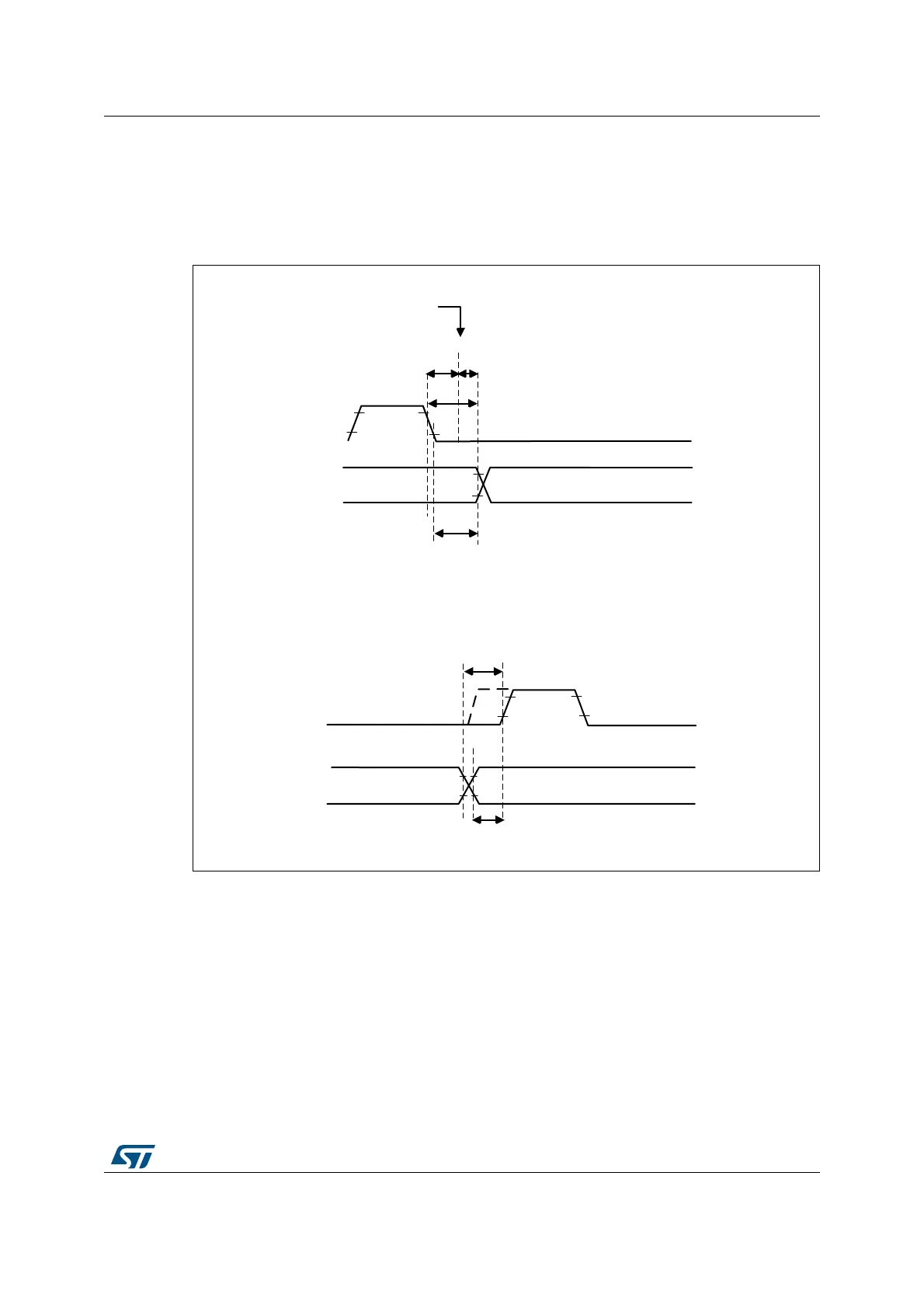

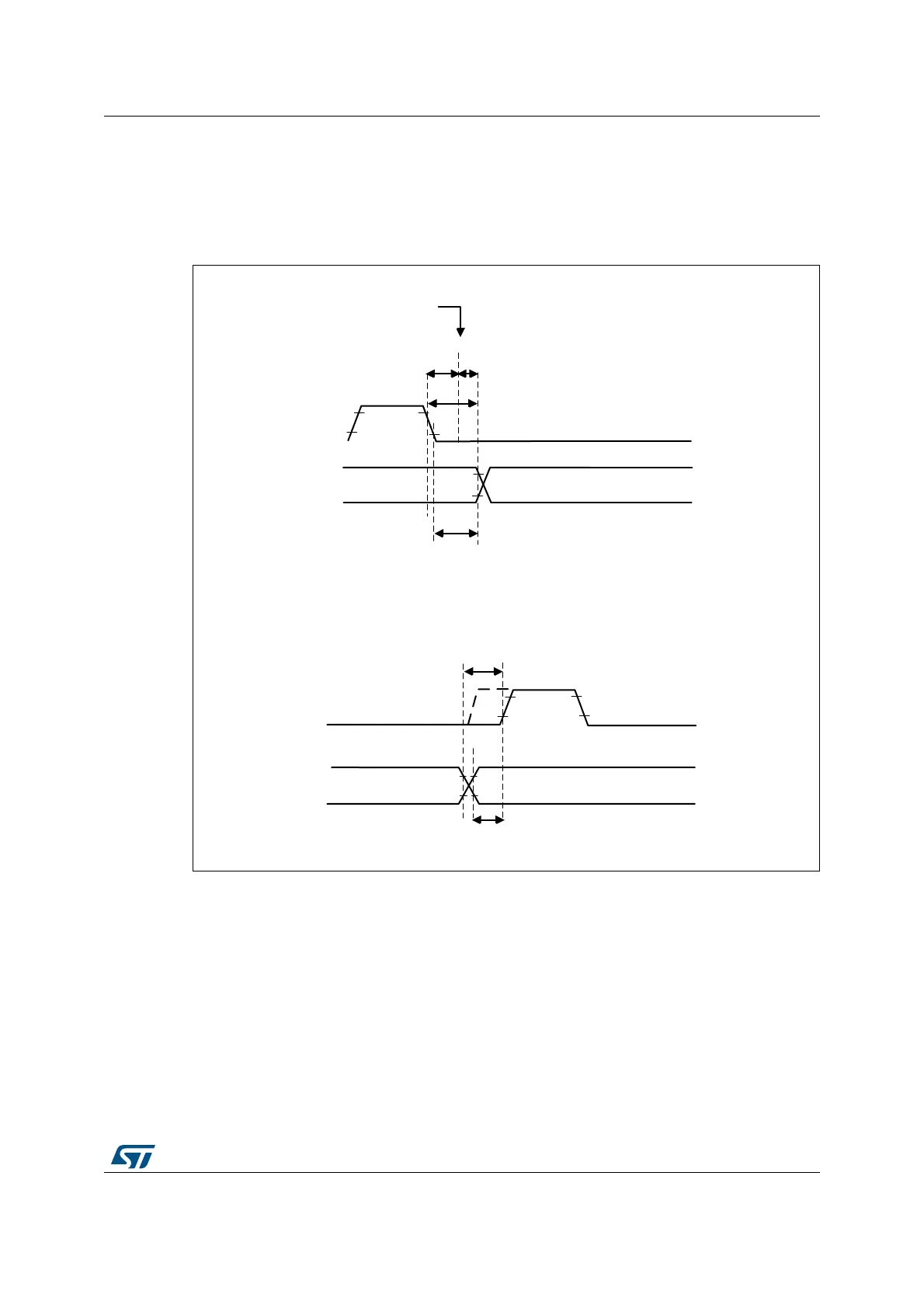

Figure 354. Setup and hold timings

• When the SCL falling edge is internally detected, a delay is inserted before sending

SDA output. This delay is

t

SDADEL

= SDADEL x t

PRESC

+ t

I2CCLK

where t

PRESC

= (PRESC+1)

x t

I2CCLK

.

T

SDADEL

impacts the hold time t

HD;DAT.

The total SDA output delay is:

t

SYNC1

+ {[SDADEL x (PRESC+1) + 1] x t

I2CCLK

}

06Y9

W

6<1&

6&/IDOOLQJHGJHLQWHUQDO

GHWHFWLRQ

6'$'(/6&/VWUHWFKHGORZE\WKH,&

6'$RXWSXWGHOD\

6&/

6'$

d,K>d/D

W

+''$7

6&/'(/

6&/VWUHWFKHGORZE\WKH,&

6&/

6'$

d^dhWd/D

W

6867$

'DWDKROGWLPHLQFDVHRIWUDQVPLVVLRQWKHGDWDLVVHQWRQ6'$RXWSXWDIWHU

WKH6'$'(/GHOD\LILWLVDOUHDG\DYDLODEOHLQ,&B7;'5

'DWDVHWXSWLPHLQFDVHRIWUDQVPLVVLRQWKH6&/'(/FRXQWHUVWDUWV

ZKHQWKHGDWDLVVHQWRQ6'$RXWSXW

Loading...

Loading...