Flexible static memory controller (FSMC) RM0351

354/1693 DocID024597 Rev 3

14.5.4 NOR Flash/PSRAM controller asynchronous transactions

Asynchronous static memories (NOR Flash, PSRAM, SRAM)

• Signals are synchronized by the internal clock HCLK. This clock is not issued to the

memory

• The FMC always samples the data before de-asserting the NOE signal. This

guarantees that the memory data hold timing constraint is met (minimum Chip Enable

high to data transition is usually 0 ns)

• If the extended mode is enabled (EXTMOD bit is set in the FMC_BCRx register), up to

four extended modes (A, B, C and D) are available. It is possible to mix A, B, C and D

modes for read and write operations. For example, read operation can be performed in

mode A and write in mode B.

• If the extended mode is disabled (EXTMOD bit is reset in the FMC_BCRx register), the

FMC can operate in Mode1 or Mode2 as follows:

– Mode 1 is the default mode when SRAM/PSRAM memory type is selected (MTYP

= 0x0 or 0x01 in the FMC_BCRx register)

– Mode 2 is the default mode when NOR memory type is selected (MTYP = 0x10 in

the FMC_BCRx register).

Mode 1 - SRAM/PSRAM (CRAM)

The next figures show the read and write transactions for the supported modes followed by

the required configuration of FMC_BCRx, and FMC_BTRx/FMC_BWTRx registers.

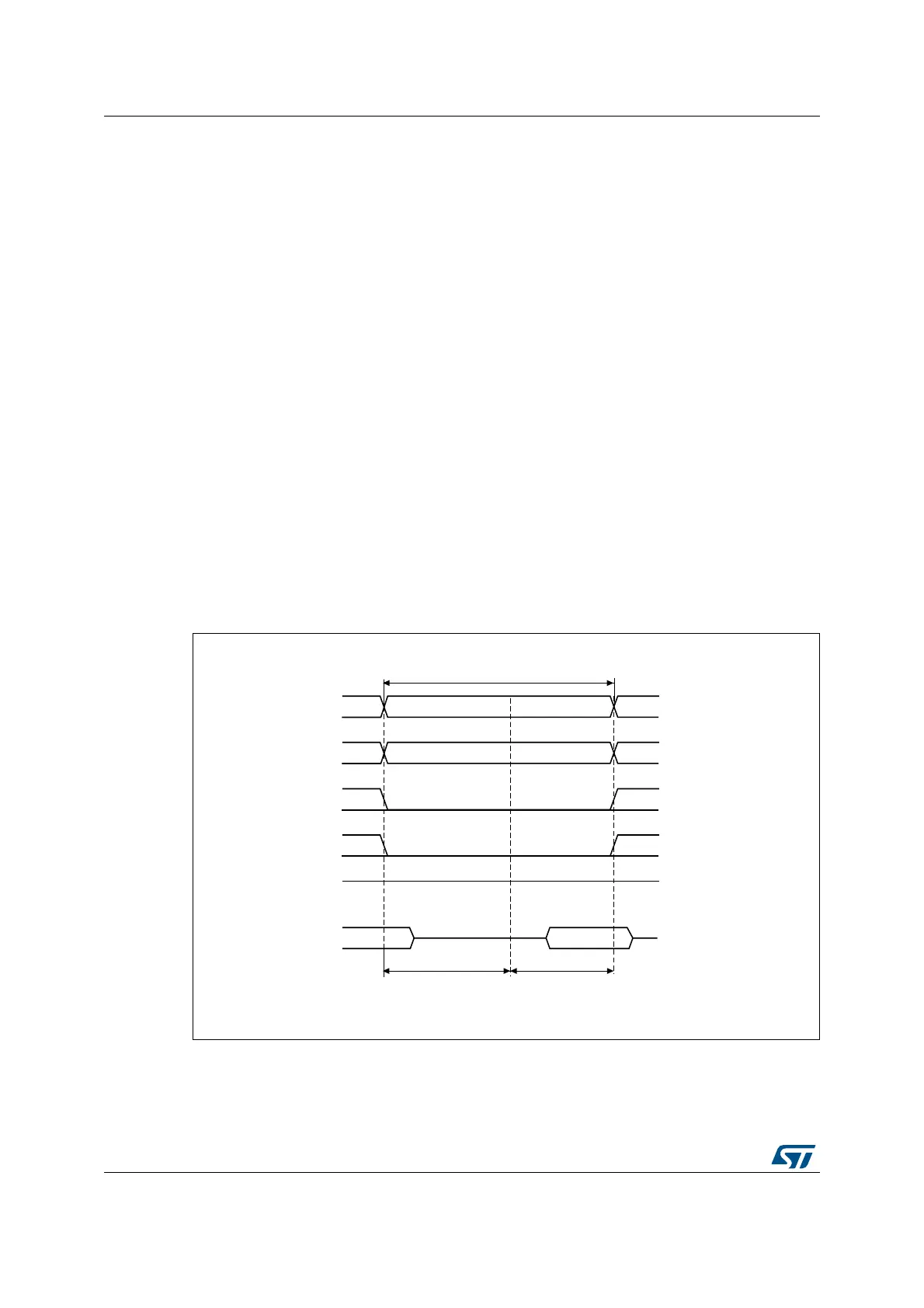

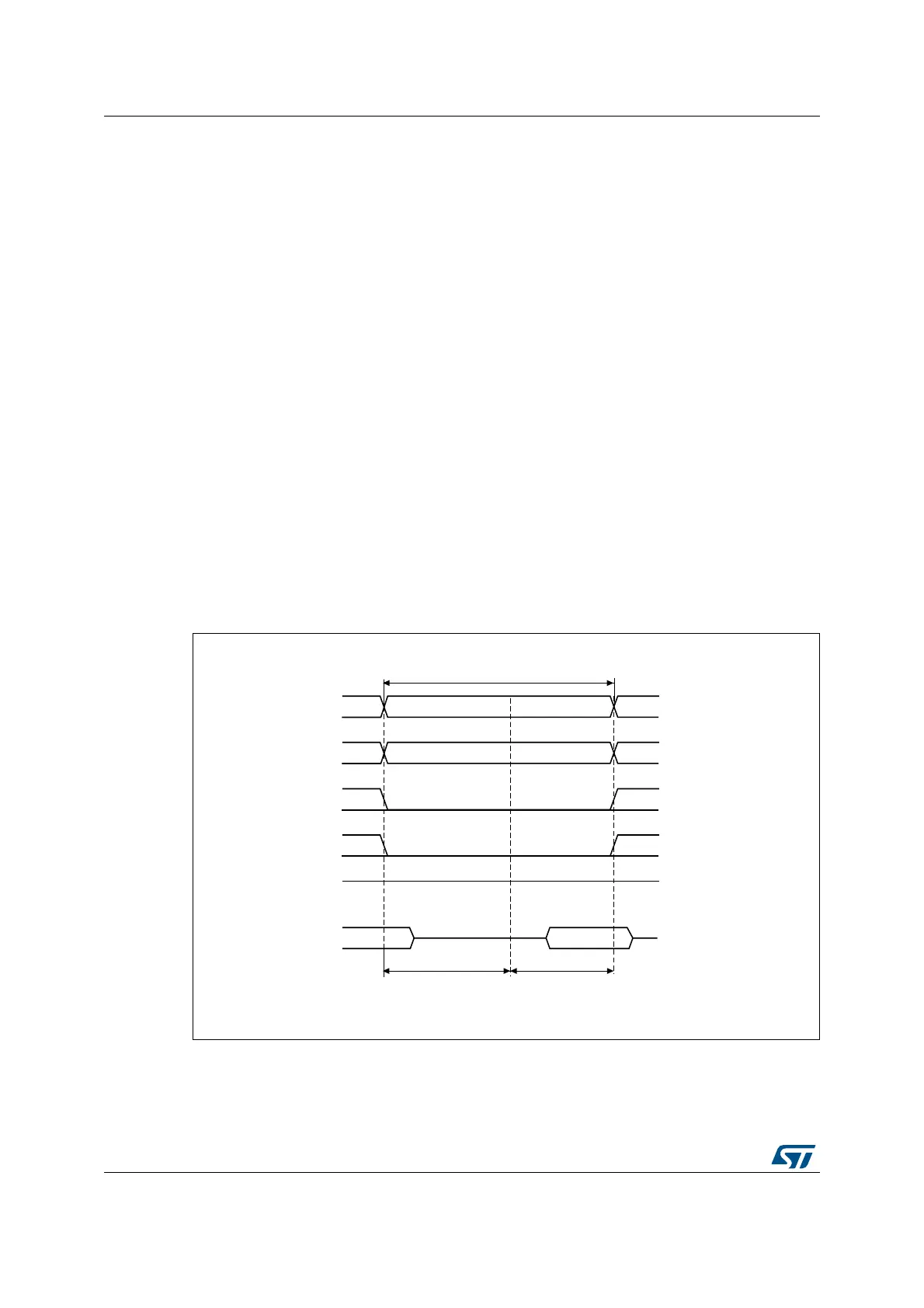

Figure 31. Mode1 read access waveforms

$>@

12(

$''6(7 '$7$67

0HPRU\WUDQVDFWLRQ

1([

'>@

+&/.F\FOHV +&/.F\FOHV

1:(

1%/>@

GDWDGULYHQ

E\PHPRU\

069

+LJK

Loading...

Loading...