DocID024597 Rev 3 1325/1693

RM0351 Serial audio interface (SAI)

1362

the case in I2S standard protocol and in MSB-justified protocol, respectively). FSOFF bit in

the SAI_xFRCR register allows to choose one of the two configurations.

FS signal role

The FS signal can have a different meaning depending on the FS function. FSDEF bit in the

SAI_xFRCR register selects which meaning it will have:

• 0: start of frame, like for instance the PCM/DSP, TDM, AC’97, audio protocols,

• 1: start of frame and channel side identification within the audio frame like for the I2S,

the MSB or LSB-justified protocols.

When the FS signal is considered as a start of frame and channel side identification within

the frame, the number of declared slots must be considered to be half the number for the left

channel and half the number for the right channel. If the number of bit clock cycles on half

audio frame is greater than the number of slots dedicated to a channel side, and TRIS = 0, 0

is sent for transmission for the remaining bit clock cycles in the SAI_xCR2 register.

Otherwise if TRIS = 1, the SD line is released to HI-Z. In reception mode, the remaining bit

clock cycles are not considered until the channel side changes.

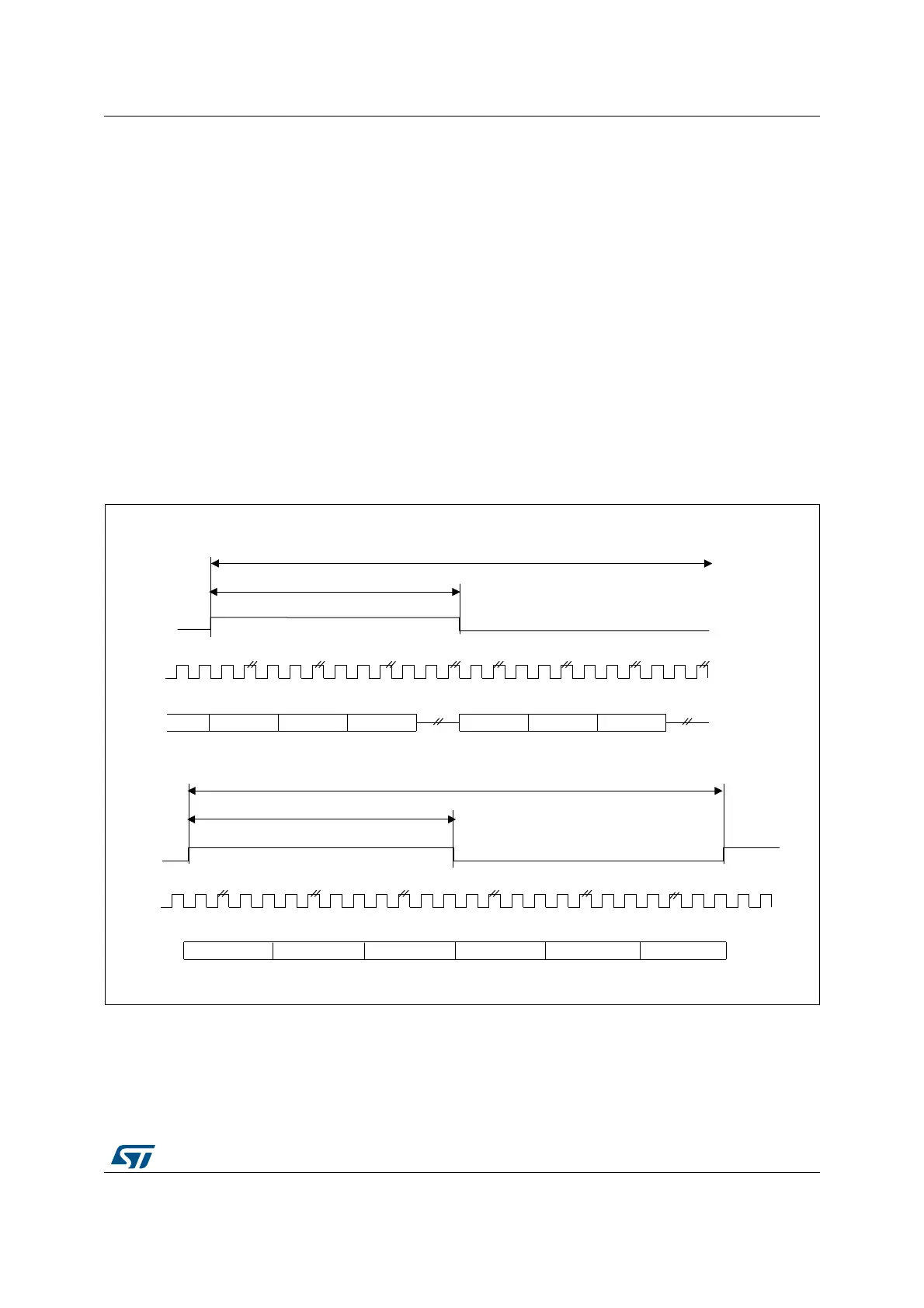

Figure 438. FS role is start of frame + channel side identification (FSDEF = TRIS = 1)

1. The frame length should be even.

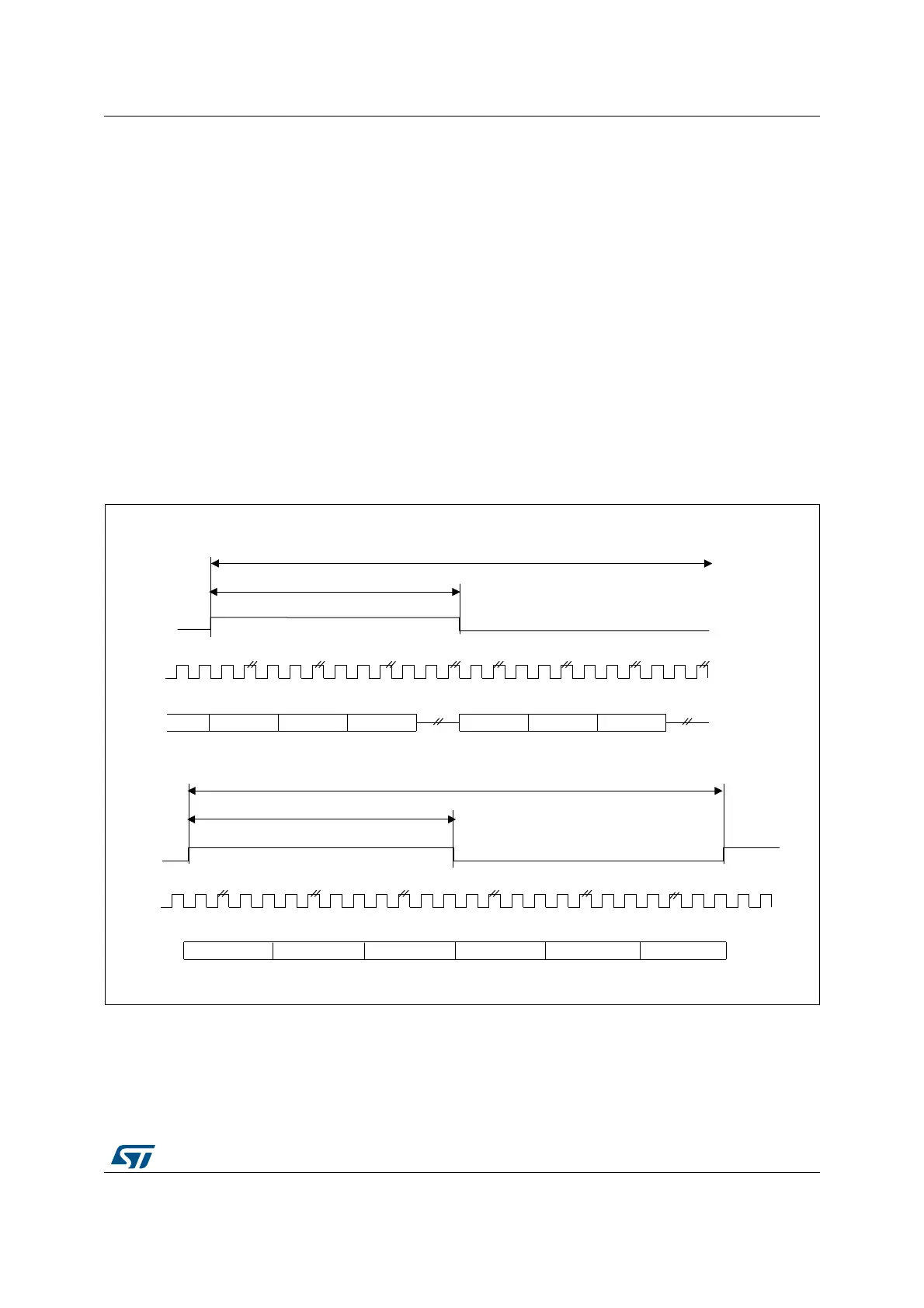

If FSDEF bit in SAI_xFRCR is kept clear, so FS signal is equivalent to a start of frame, and if

the number of slots defined in NBSLOT[3:0] in SAI_xSLOTR multiplied by the number of bits

by slot configured in SLOTSZ[1:0] in SAI_xSLOTR is less than the frame size (bit FRL[7:0]

in the SAI_xFRCR register), then:

VFN

VORW

$XGLRIUDPH

)6

+DOIRIIUDPH

$XGLRIUDPH

)6

+DOIRIIUDPH

1XPEHURIVORWVQRWDOLJQHGZLWKWKHDXGLRIUDPH

1XPEHURIVORWVDOLJQHGZLWKWKHDXGLRIUDPH

069

6ORW

VFN

VORW

6ORW 6ORW

6ORW 6ORW6ORW

6ORW21 6ORW2))

6ORW21

6ORW21 6ORW2)) 6ORW21

Loading...

Loading...