DocID024597 Rev 3 1469/1693

RM0351 Controller area network (bxCAN)

1494

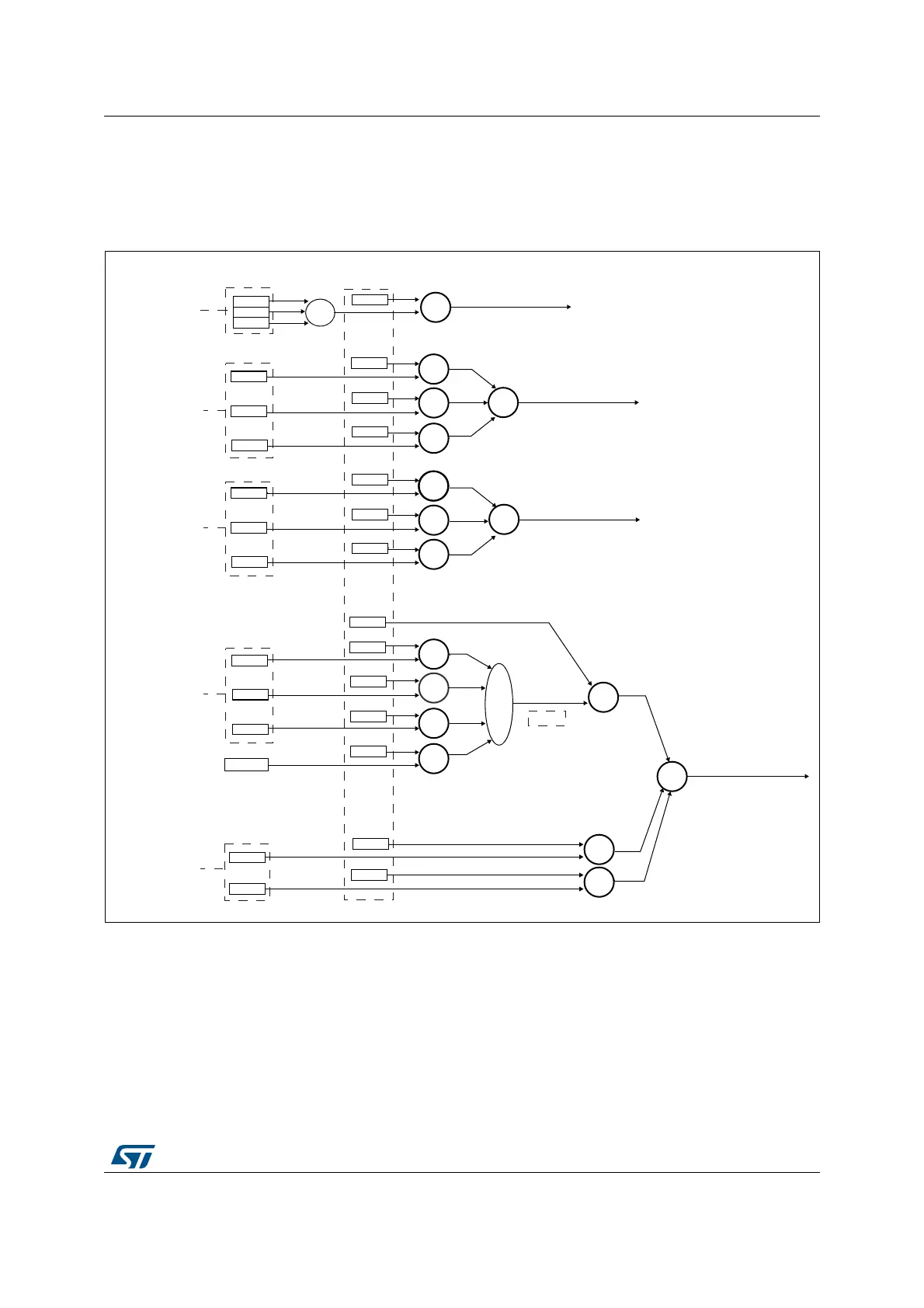

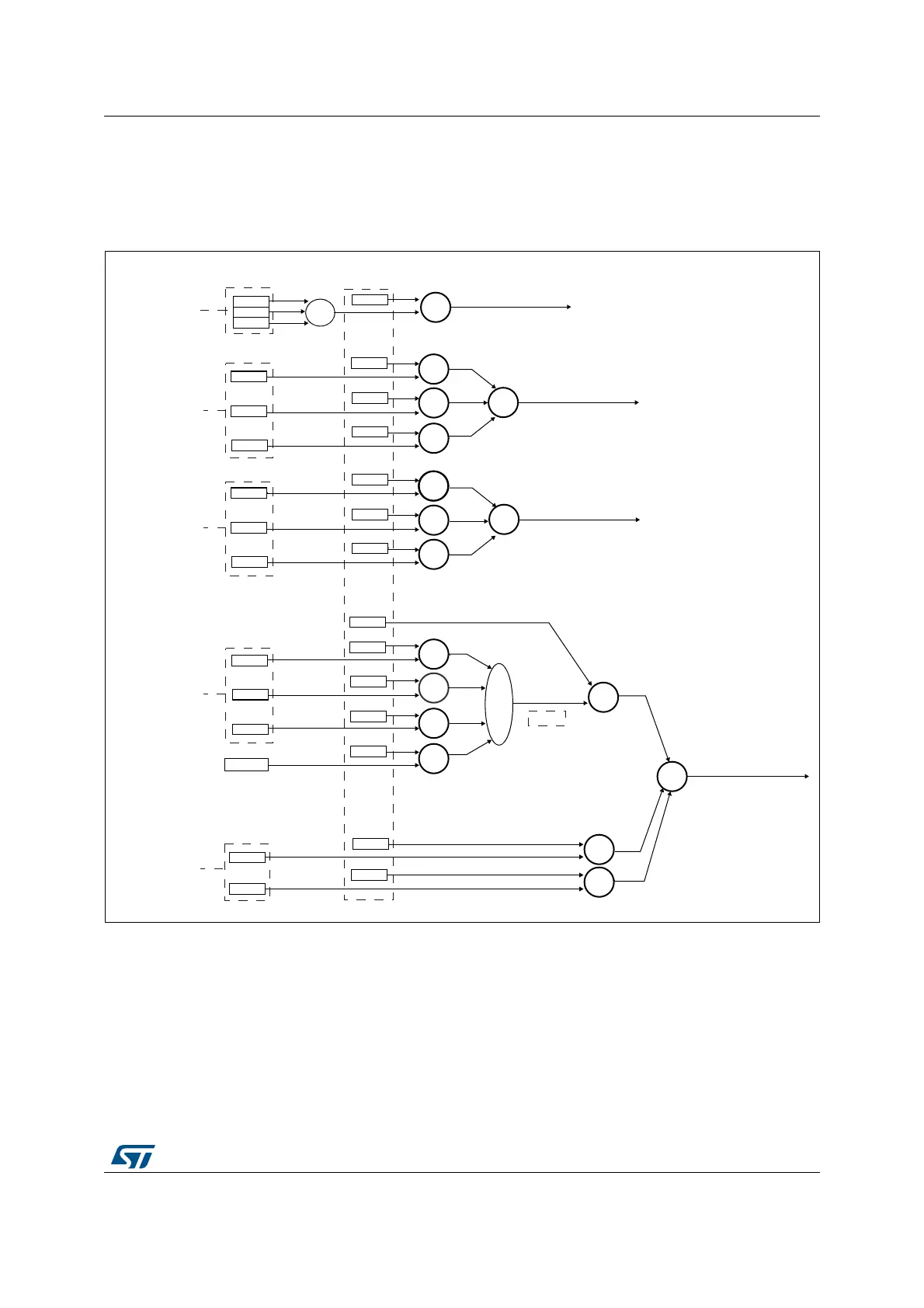

42.8 bxCAN interrupts

Four interrupt vectors are dedicated to bxCAN. Each interrupt source can be independently

enabled or disabled by means of the CAN Interrupt Enable Register (CAN_IER).

Figure 491. Event flags and interrupt generation

• The transmit interrupt can be generated by the following events:

– Transmit mailbox 0 becomes empty, RQCP0 bit in the CAN_TSR register set.

– Transmit mailbox 1 becomes empty, RQCP1 bit in the CAN_TSR register set.

– Transmit mailbox 2 becomes empty, RQCP2 bit in the CAN_TSR register set.

• The FIFO 0 interrupt can be generated by the following events:

– Reception of a new message, FMP0 bits in the CAN_RF0R register are not ‘00’.

– FIFO0 full condition, FULL0 bit in the CAN_RF0R register set.

– FIFO0 overrun condition, FOVR0 bit in the CAN_RF0R register set.

&$1B765

75$160,7

,17(55837

)03,(

)29,(

(:*,(

(39)

%2))

%2),(

/(&

)03,(

)29,(

),)2

,17(55837

:.8,(

6/$.,

&$1B065

069

),)2

,17(55837

67$786&+$1*(

(5525

,17(55837

70(,(

)),(

)),(

(55,(

(39,(

/(&,(

6/.,(

(:*)

(55,(

54&3

54&3

54&3

)03

)8//

)295

)03

)8//

)295

&$1B5)5

&$1B5)5

&$1B(65

&$1B065

&$1B,(5

:.8,

Loading...

Loading...