USB on-the-go full-speed (OTG_FS) RM0351

1544/1693 DocID024597 Rev 3

43.15.14 OTG core LPM configuration register (OTG_GLPMCFG)

Address offset: 0x54

Reset value: 0x0000 0000

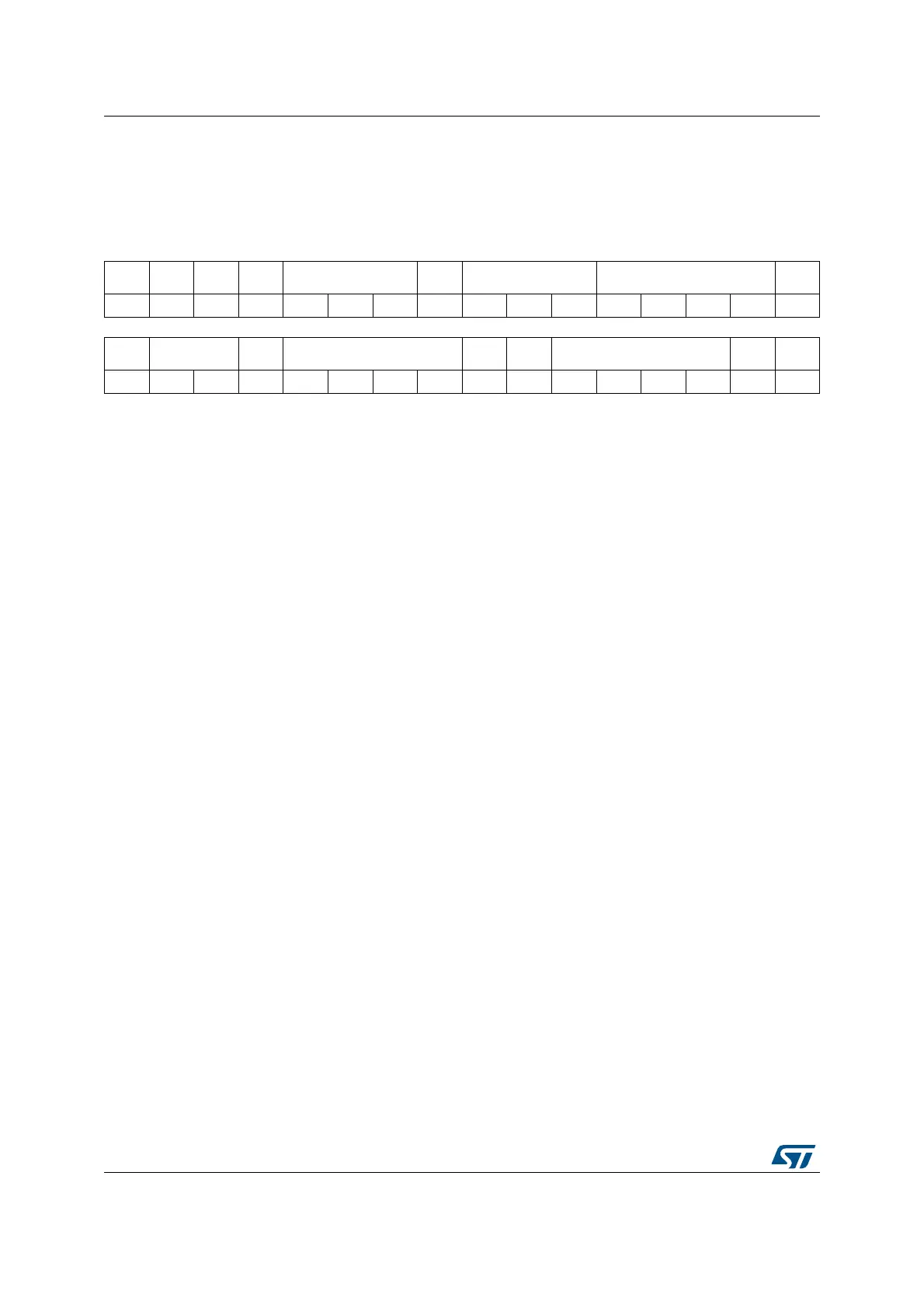

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res.

EN

BESL

LPMRCNTSTS

SND

LPM

LPMRCNT LPMCHIDX

L1RSM

OK

rw r r r rsrwrwrwrwrwrwrw r

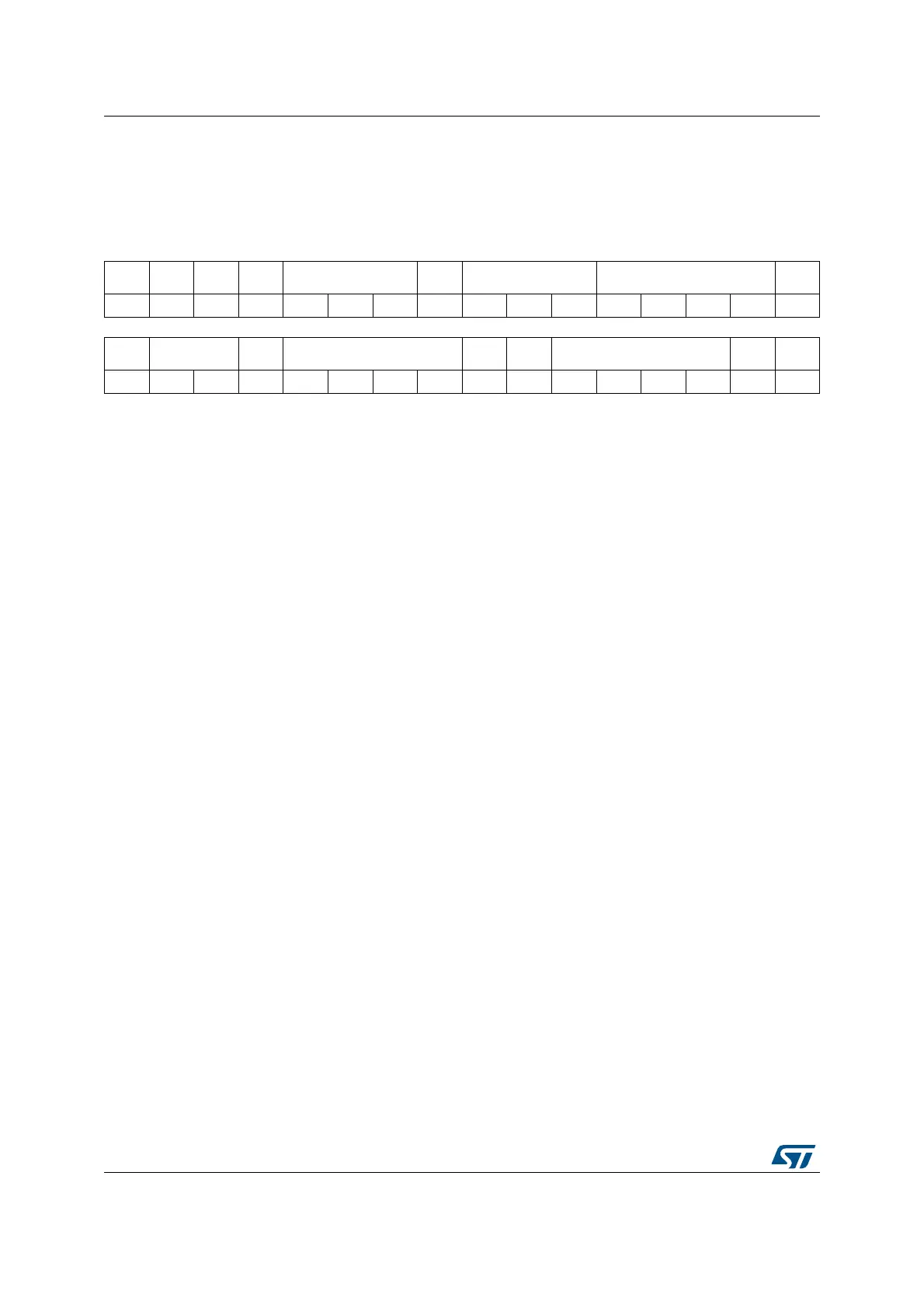

1514131211109876543210

SLP

STS

LPMRSP

L1DS

EN

BESLTHRS

L1SS

EN

REM

WAKE

BESL

LPM

ACK

LPM

EN

r r r rw rw rw rw rw rw rw/r rw/r rw/r rw/r rw/r rw rw

Bits 31:29 Reserved, must be kept at reset value.

Bit 28 ENBESL: Enable best effort service latency

This bit enables the BESL feature as defined in the LPM errata:

0:The core works as described in the following document:

USB 2.0 Link Power Management Addendum Engineering Change Notice to the USB 2.0

specification, July 16, 2007

1:The core works as described in the LPM Errata:

Errata for USB 2.0 ECN: Link Power Management (LPM) - 7/2007

Note: Only the updated behavior (described in LPM Errata) is considered in this document

and so the ENBESL bit should be set to '1' by application SW.

Bits 27:25 LPMRCNTSTS: LPM retry count status

Number of LPM host retries still remaining to be transmitted for the current LPM sequence.

Note: Accessible only in host mode.

Bit 24 SNDLPM: Send LPM transaction

When the application software sets this bit, an LPM transaction containing two tokens, EXT

and LPM is sent. The hardware clears this bit once a valid response (STALL, NYET, or

ACK) is received from the device or the core has finished transmitting the programmed

number of LPM retries.

Note: This bit must be set only when the host is connected to a local port.

Note: Accessible only in host mode.

Bits 23:21 LPMRCNT: LPM retry count

When the device gives an ERROR response, this is the number of additional LPM retries

that the host performs until a valid device response (STALL, NYET, or ACK) is received.

Note: Accessible only in host mode.

Bits 20:17 LPMCHIDX: LPM Channel Index

The channel number on which the LPM transaction has to be applied while sending an LPM

transaction to the local device. Based on the LPM channel index, the core automatically

inserts the device address and endpoint number programmed in the corresponding channel

into the LPM transaction.

Note: Accessible only in host mode.

Loading...

Loading...