DocID024597 Rev 3 991/1693

RM0351 General-purpose timers (TIM15/16/17)

1009

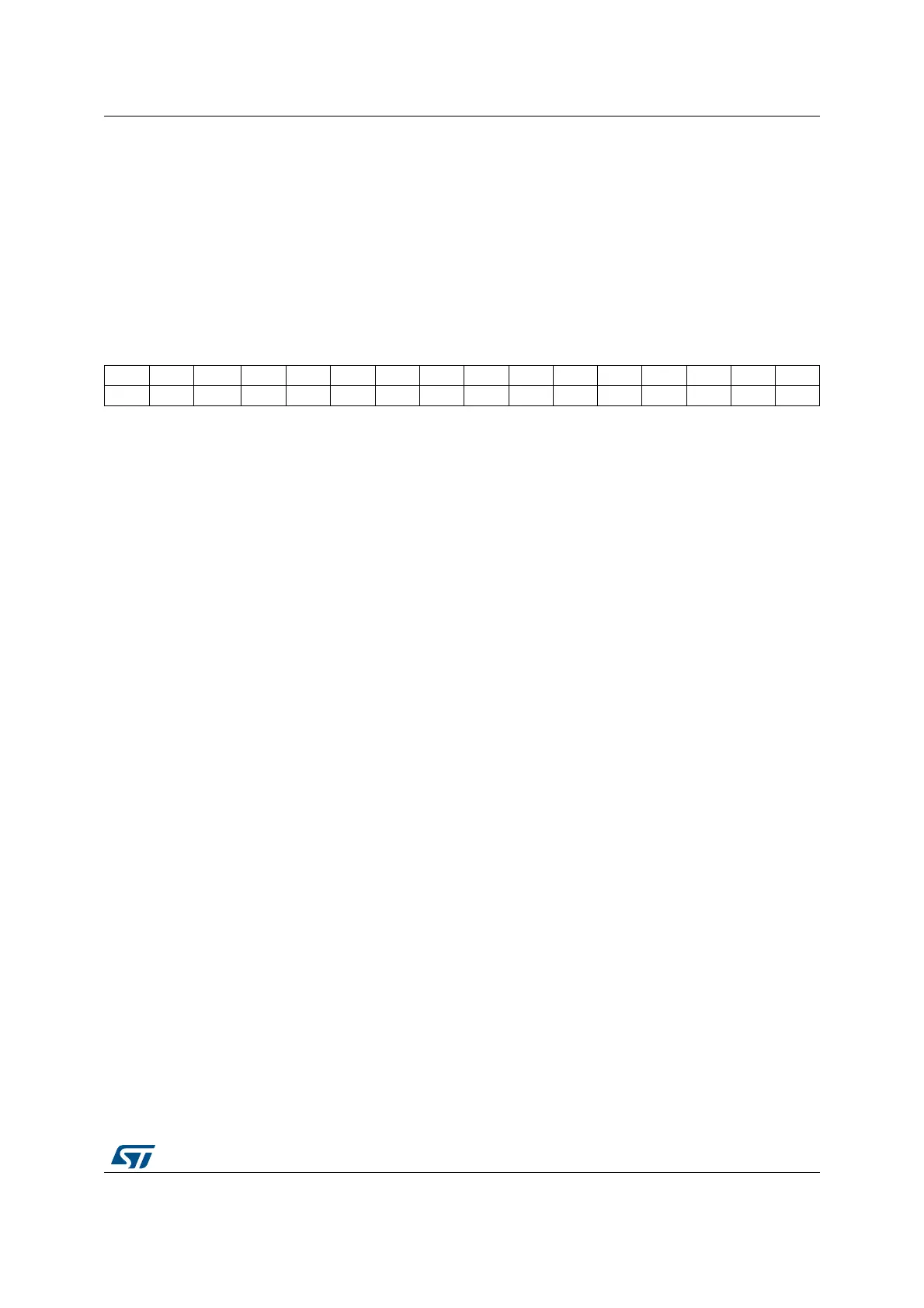

28.6.3 TIM16&TIM17 DMA/interrupt enable register (TIMx_DIER)

Address offset: 0x0C

Reset value: 0x0000

Bit 0 CCPC: Capture/compare preloaded control

0: CCxE, CCxNE and OCxM bits are not preloaded

1: CCxE, CCxNE and OCxM bits are preloaded, after having been written, they are updated

only when COM bit is set.

Note: This bit acts only on channels that have a complementary output.

1514131211109876543210

Res TDE COMDE Res Res Res CC1DE UDE BIE Res COMIE Res Res Res CC1IE UIE

rw rw rw rw rw rw rw rw

Bit 15 Reserved, must be kept at reset value.

Bit 14 TDE: Trigger DMA request enable

0: Trigger DMA request disabled

1: Trigger DMA request enabled

Bit 13 COMDE: COM DMA request enable

0: COM DMA request disabled

1: COM DMA request enabled

Bits 12:10 Reserved, must be kept at reset value.

Bit 9 CC1DE: Capture/Compare 1 DMA request enable

0: CC1 DMA request disabled

1: CC1 DMA request enabled

Bit 8 UDE: Update DMA request enable

0: Update DMA request disabled

1: Update DMA request enabled

Bit 7 BIE: Break interrupt enable

0: Break interrupt disabled

1: Break interrupt enabled

Bit 6 Reserved, must be kept at reset value.

Bit 5 COMIE: COM interrupt enable

0: COM interrupt disabled

1: COM interrupt enabled

Bits 4:2 Reserved, must be kept at reset value.

Bit 1 CC1IE: Capture/Compare 1 interrupt enable

0: CC1 interrupt disabled

1: CC1 interrupt enabled

Bit 0 UIE: Update interrupt enable

0: Update interrupt disabled

1: Update interrupt enabled

Loading...

Loading...