SD/SDIO/MMC card host interface (SDMMC) RM0351

1400/1693 DocID024597 Rev 3

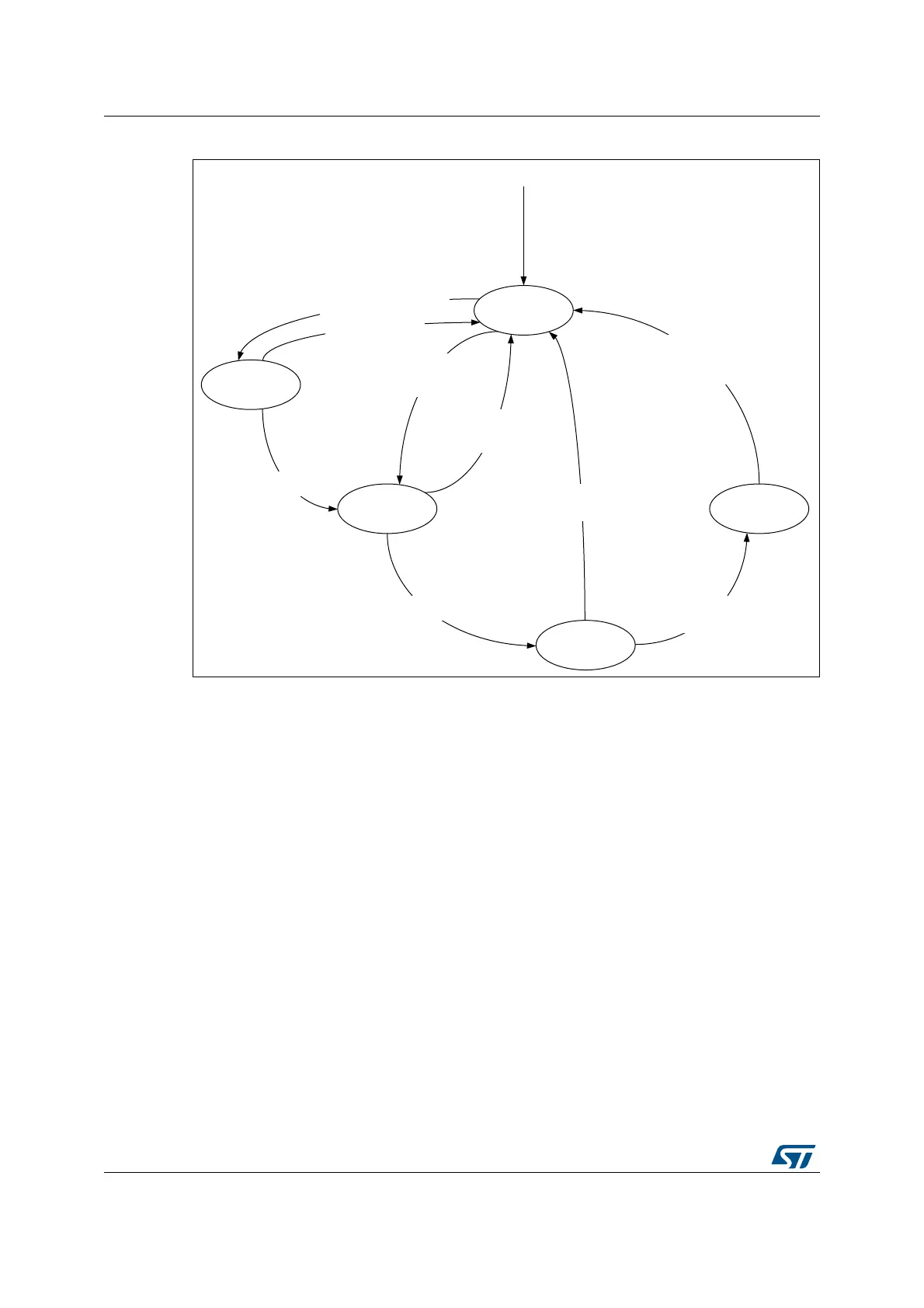

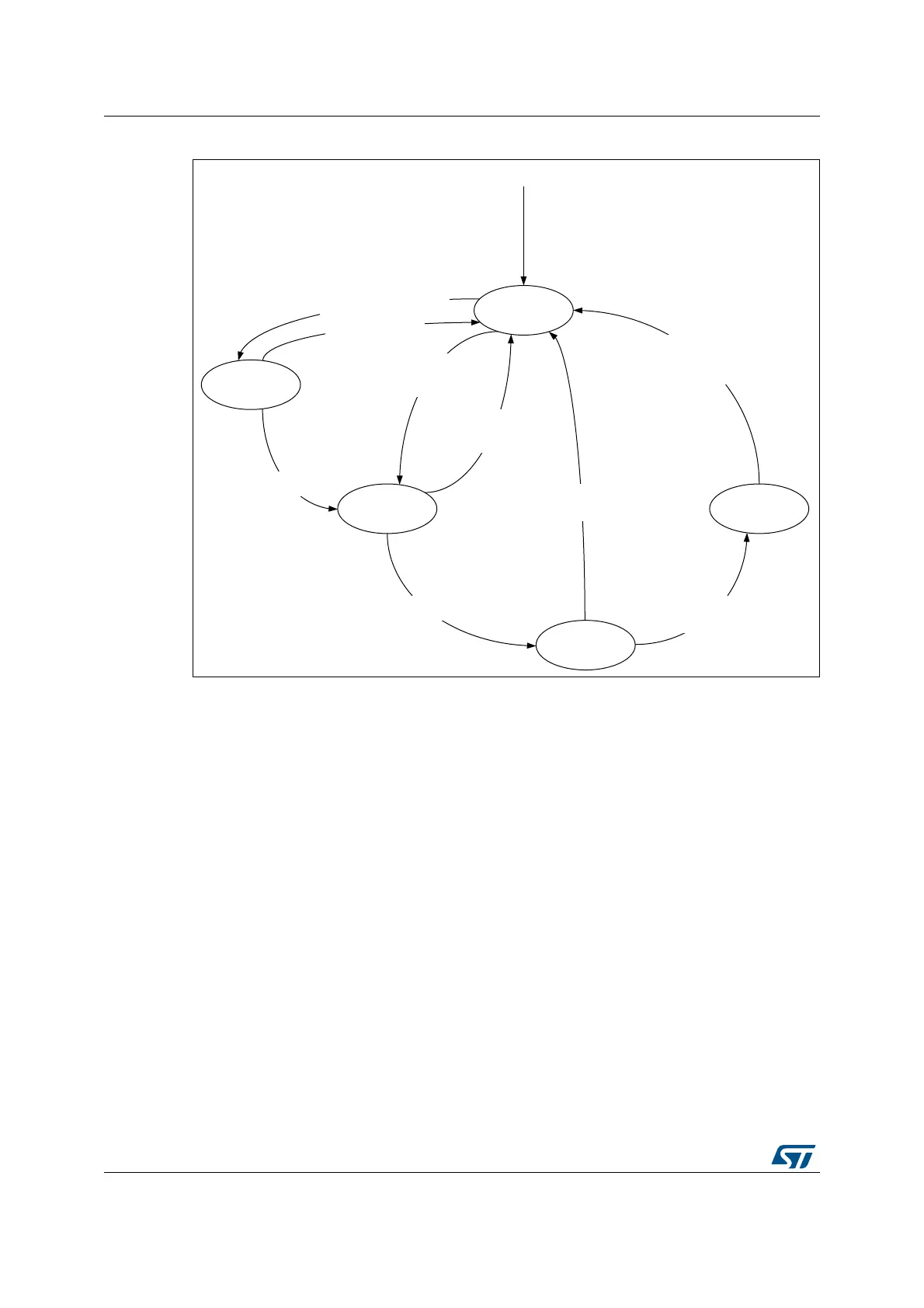

Figure 474. Command path state machine (SDMMC)

When the Wait state is entered, the command timer starts running. If the timeout is reached

before the CPSM moves to the Receive state, the timeout flag is set and the Idle state is

entered.

Note: The command timeout has a fixed value of 64 SDMMC_CK clock periods.

If the interrupt bit is set in the command register, the timer is disabled and the CPSM waits

for an interrupt request from one of the cards. If a pending bit is set in the command register,

the CPSM enters the Pend state, and waits for a CmdPend signal from the data path

subunit. When CmdPend is detected, the CPSM moves to the Send state. This enables the

data counter to trigger the stop command transmission.

Note: The CPSM remains in the Idle state for at least eight SDMMC_CK periods to meet the N

CC

and N

RC

timing constraints. N

CC

is the minimum delay between two host commands, and

N

RC

is the minimum delay between the host command and the card response.

069

,GOH

5HFHLYH

3HQG

6HQG

:DLW

5HVSRQVHUHFHLYHGRU

GLVDEOHGRUFRPPDQG

&5&IDLOHG

5HVSRQVH

VWDUWHG

&360GLVDEOHG

RUQRUHVSRQVH

(QDEOHGDQG

FRPPDQGVWDUW

&360HQDEOHGDQG

SHQGLQJFRPPDQG

/DVWGDWD

2QUHVHW

:DLWIRUUHVSRQVH

&360GLVDEOHGRU

FRPPDQGWLPHRXW

&360GLVDEOHG

Loading...

Loading...