DocID024597 Rev 3 637/1693

RM0351 Digital filter for sigma delta modulators (DFSDM)

657

21.7.2 DFSDM control register 2 (DFSDMx_CR2)

Address offset: 0x100 * (x+1) + 0x004, x = 0...3

Reset value: 0x0000 0000

Bit 2 Reserved, must be kept at reset value.

Bit 1 JSWSTART: Start a conversion of the injected group of channels

0: Writing ‘0’ has no effect.

1: Writing ‘1’ makes a request to convert the channels in the injected conversion group, causing

JCIP to become ‘1’ at the same time. If JCIP=1 already, then writing to JSWSTART has no effect.

Writing ‘1’ has no effect if JSYNC=1.

This bit is always read as ‘0’.

Bit 0 DFEN: DFSDM enable

0: DFSDMx is disabled. All conversions of given DFSDMx are stopped immediately and all DFSDMx

functions are stopped.

1: DFSDMx is enabled. If DFSDMx is enabled, then DFSDM starts operating according to its setting.

Data is cleared by setting DFEN=0:

–register DFSDMx_ISR is set to the reset state

–register DFSDMx_AWSR is set to the reset state

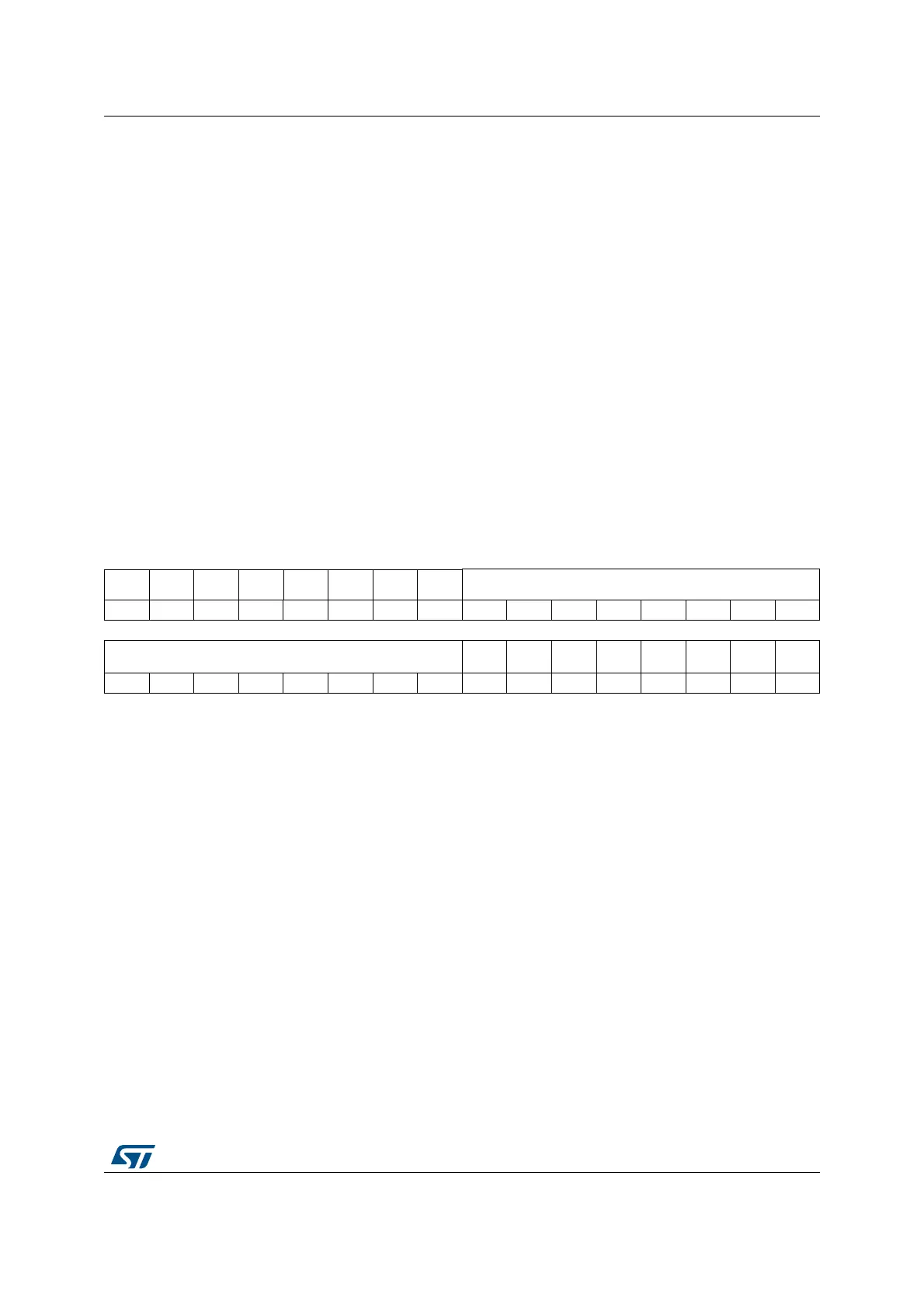

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. AWDCH[7:0]

rw rw rw rw rw rw rw rw

1514131211109876543210

EXCH[7:0] Res.

CKAB

IE

SCDIE AWDIE

ROVR

IE

JOVRI

E

REOC

IE

JEOCI

E

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:16 AWDCH[7:0]: Analog watchdog channel selection

These bits select the input channel to be guarded continuously by the analog watchdog

AWDCH[y] = 0: Analog watchdog is disabled on channel y

AWDCH[y] = 1: Analog watchdog is enabled on channel y

Bits 15:8 EXCH[7:0]: Extremes detector channel selection

These bits select the input channels to be taken by the Extremes detector

EXCH[y] = 0: Extremes detector does not accept data from channel y

EXCH[y] = 1: Extremes detector accepts data from channel y

Bit 7 Reserved, must be kept at reset value.

Bit 6 CKABIE: Clock absence interrupt enable

0: Detection of channel input clock absence interrupt is disabled

1: Detection of channel input clock absence interrupt is enabled

Please see the explanation of CKABF[7:0] in DFSDMx_ISR.

Note: CKABIE is present only in DFSDM0_CR2 register (filter x=0)

Loading...

Loading...