DocID024597 Rev 3 1089/1693

RM0351 Real-time clock (RTC)

1106

34.6.5 RTC prescaler register (RTC_PRER)

This register must be written in initialization mode only. The initialization must be performed

in two separate write accesses. Refer to Calendar initialization and configuration on

page 1070.

This register is write protected. The write access procedure is described in RTC register

write protection on page 1070.

Address offset: 0x10

Backup domain reset value: 0x007F 00FF

System reset: not affected

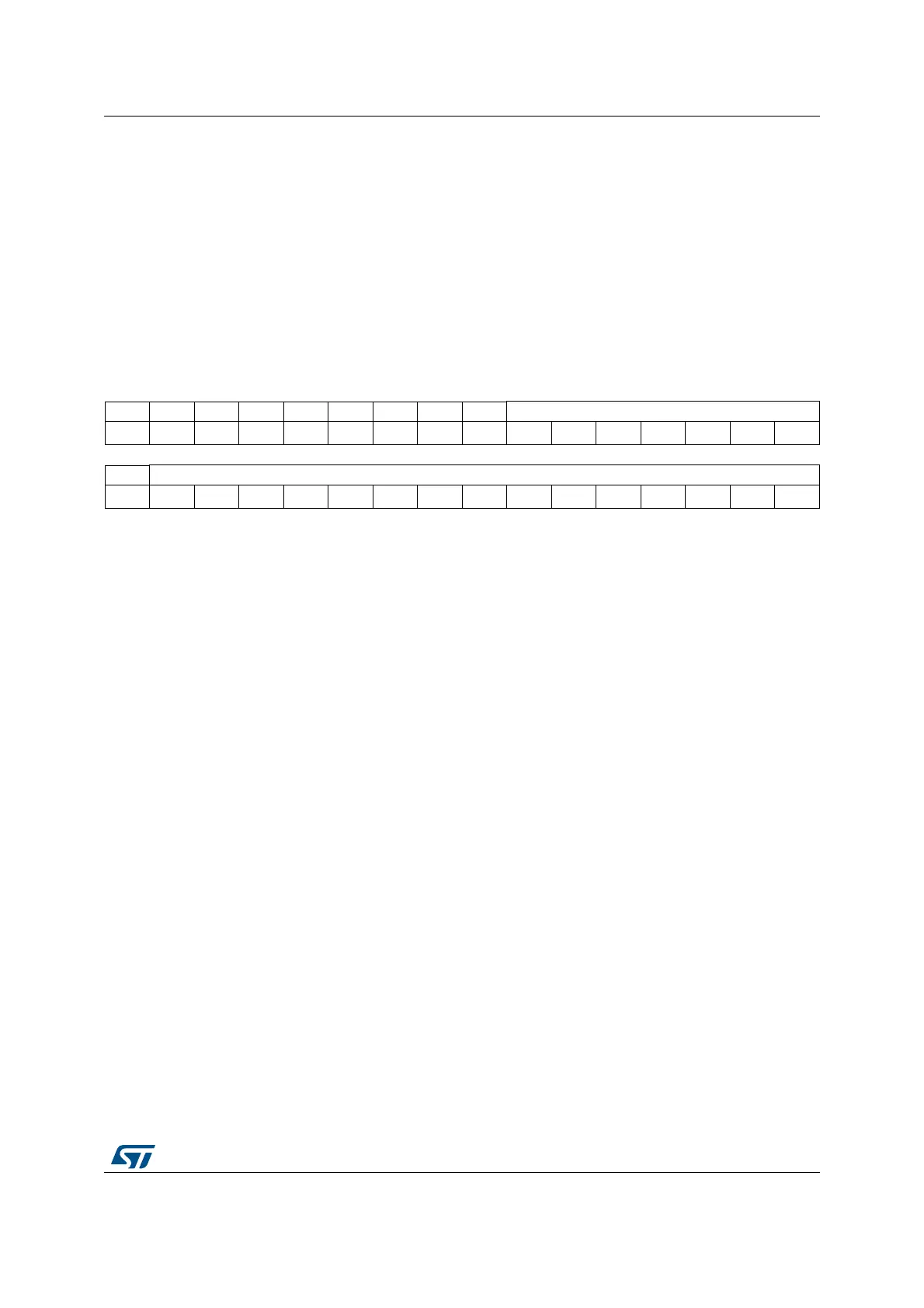

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. PREDIV_A[6:0]

rw rw rw rw rw rw rw

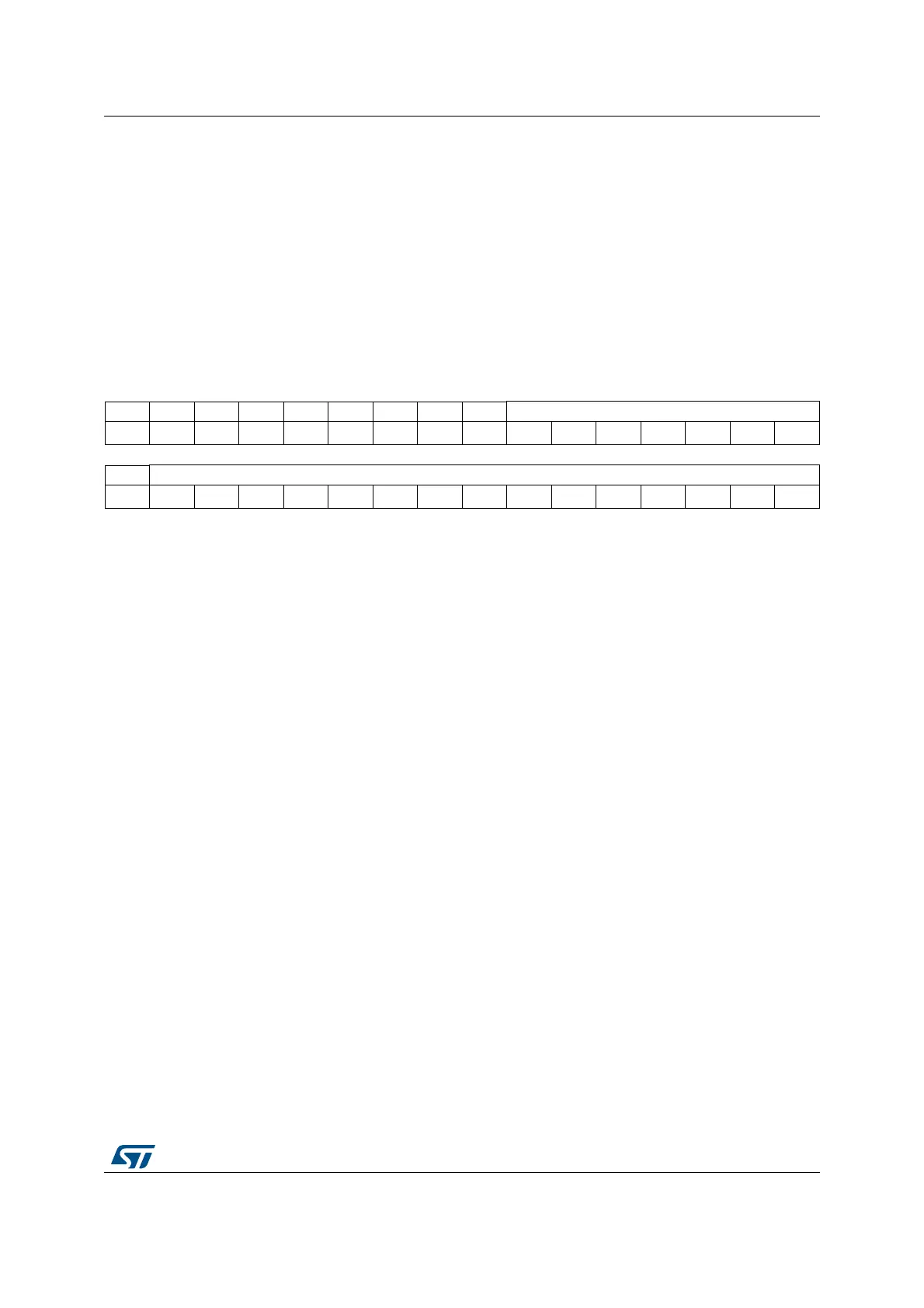

1514131211109876543210

Res. PREDIV_S[14:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:23 Reserved, must be kept at reset value

Bits 22:16 PREDIV_A[6:0]: Asynchronous prescaler factor

This is the asynchronous division factor:

ck_apre frequency = RTCCLK frequency/(PREDIV_A+1)

Bit 15 Reserved, must be kept at reset value.

Bits 14:0 PREDIV_S[14:0]: Synchronous prescaler factor

This is the synchronous division factor:

ck_spre frequency = ck_apre frequency/(PREDIV_S+1)

Loading...

Loading...