General-purpose timers (TIM2/TIM3/TIM4/TIM5) RM0351

926/1693 DocID024597 Rev 3

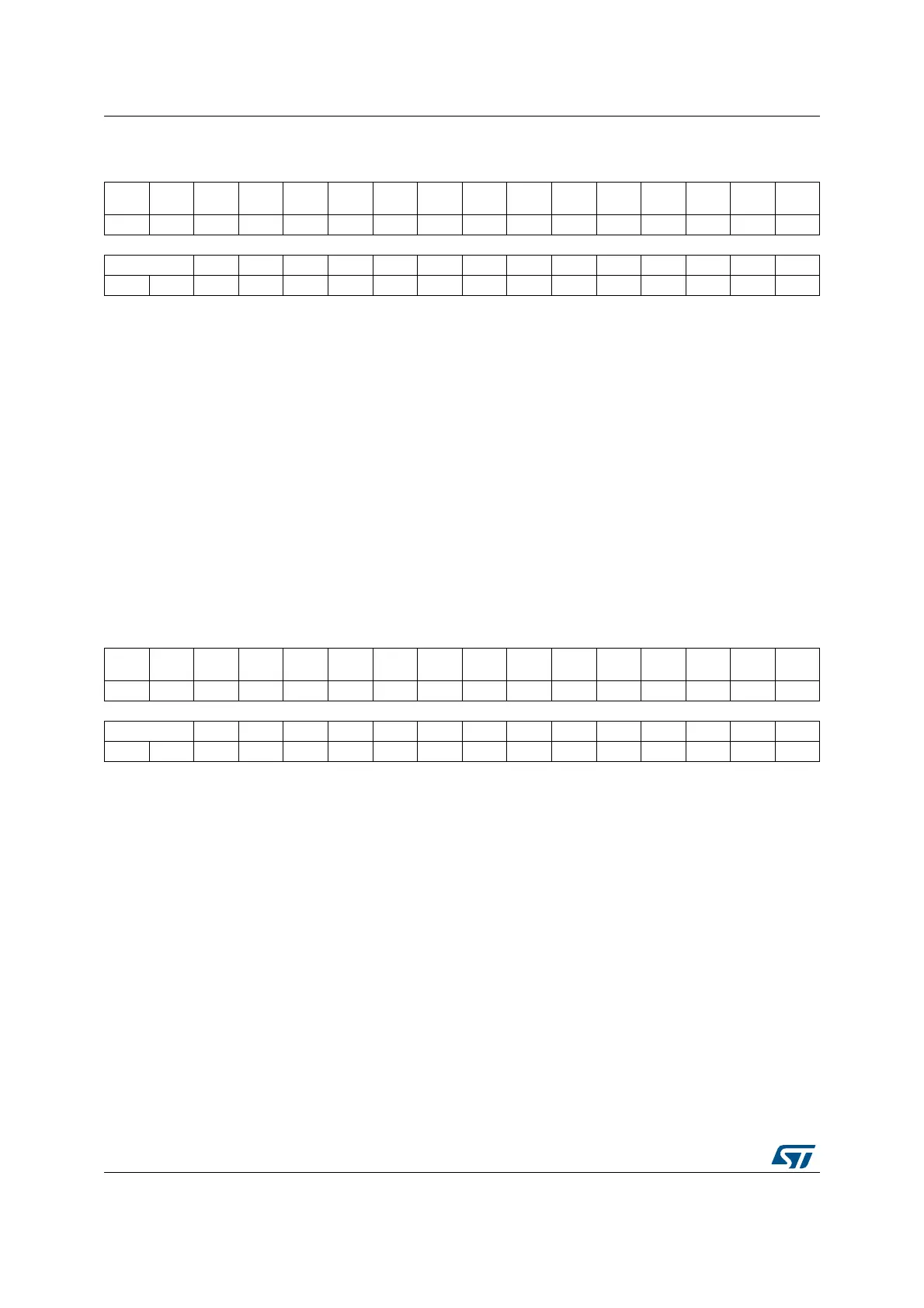

Reset value: 0x0000

27.4.22 TIM3 option register 2 (TIM3_OR2)

Address offset: 0x60

Reset value: 0x0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

ETR

SEL2

rw

1514131211109876543210

ETRSEL[1:0] Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw rw

Bits 31:17 Reserved, must be kept at reset value.

Bits 16:14 ETRSEL[2:0]: ETR source selection

These bits select the ETR input source.

000: ETR legacy mode

001: COMP1 output connected to ETR input

010: COMP2 output connected to ETR input

Other: reserved

Note: These bits can not be modified as long as LOCK level 1 has been programmed (LOCK

bits in TIMx_BDTR register).

Bits 13:0 Reserved, must be kept at reset value.

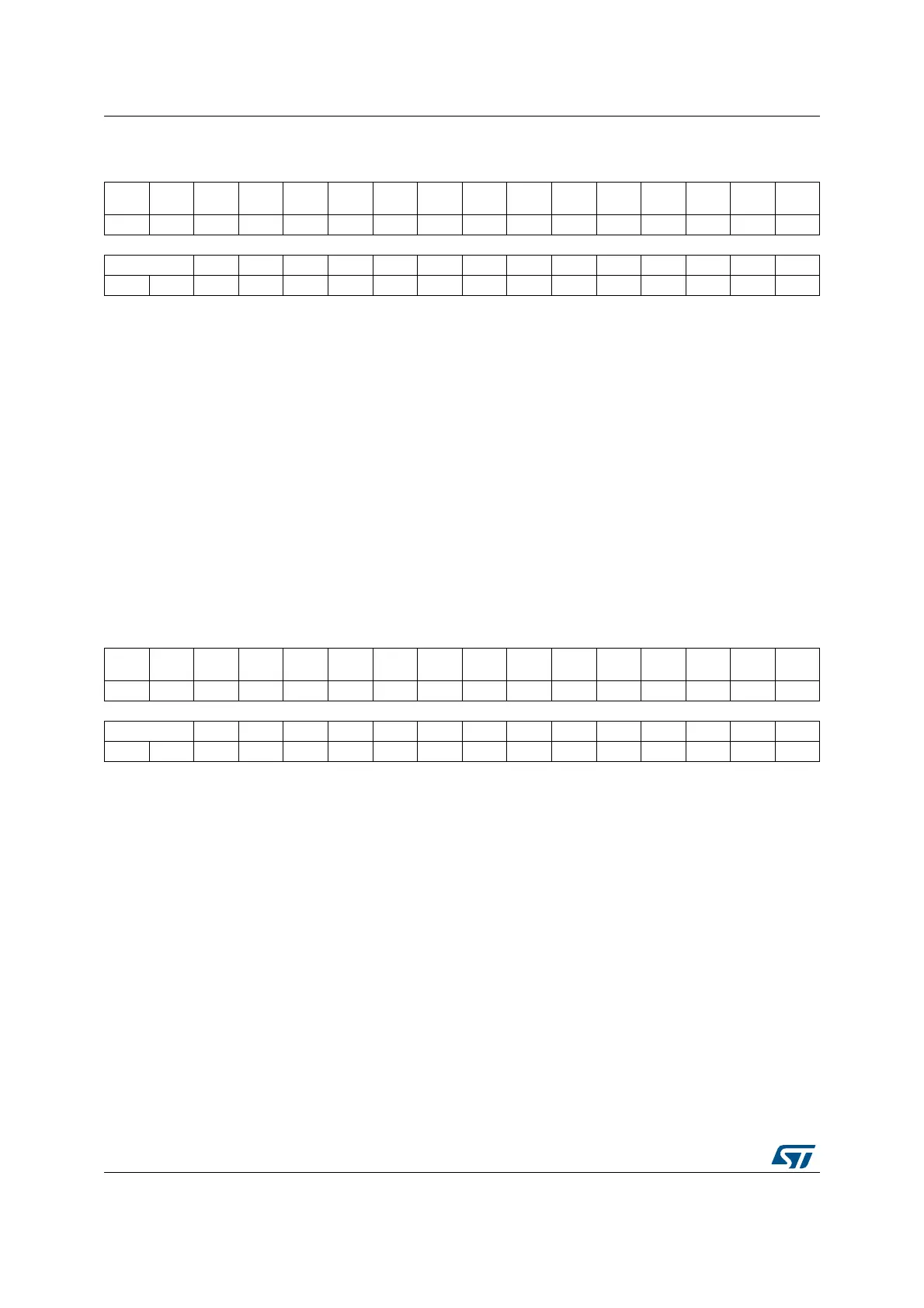

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

ETR

SEL2

rw

1514131211109876543210

ETRSEL[1:0] Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw rw

Bits 31:17 Reserved, must be kept at reset value.

Bits 16:14 ETRSEL[2:0]: ETR source selection

These bits select the ETR input source.

000: ETR legacy mode

001: COMP1 output connected to ETR input

Other: reserved

Note: These bits can not be modified as long as LOCK level 1 has been programmed (LOCK

bits in TIMx_BDTR register).

Bits 13:0 Reserved, must be kept at reset value.

Loading...

Loading...