Serial peripheral interface (SPI) RM0351

1308/1685 DocID024597 Rev 3

If the SPI is disabled during a communication the following sequence must be followed:

1. Disable the SPI

2. Clear the CRCEN bit

3. Enable the CRCEN bit

4. Enable the SPI

Note: When the SPI is in slave mode, the CRC calculator is sensitive to the SCK slave input clock

as soon as the CRCEN bit is set, and this is the case whatever the value of the SPE bit. In

order to avoid any wrong CRC calculation, the software must enable CRC calculation only

when the clock is stable (in steady state). When the SPI interface is configured as a slave,

the NSS internal signal needs to be kept low between the data phase and the CRC phase.

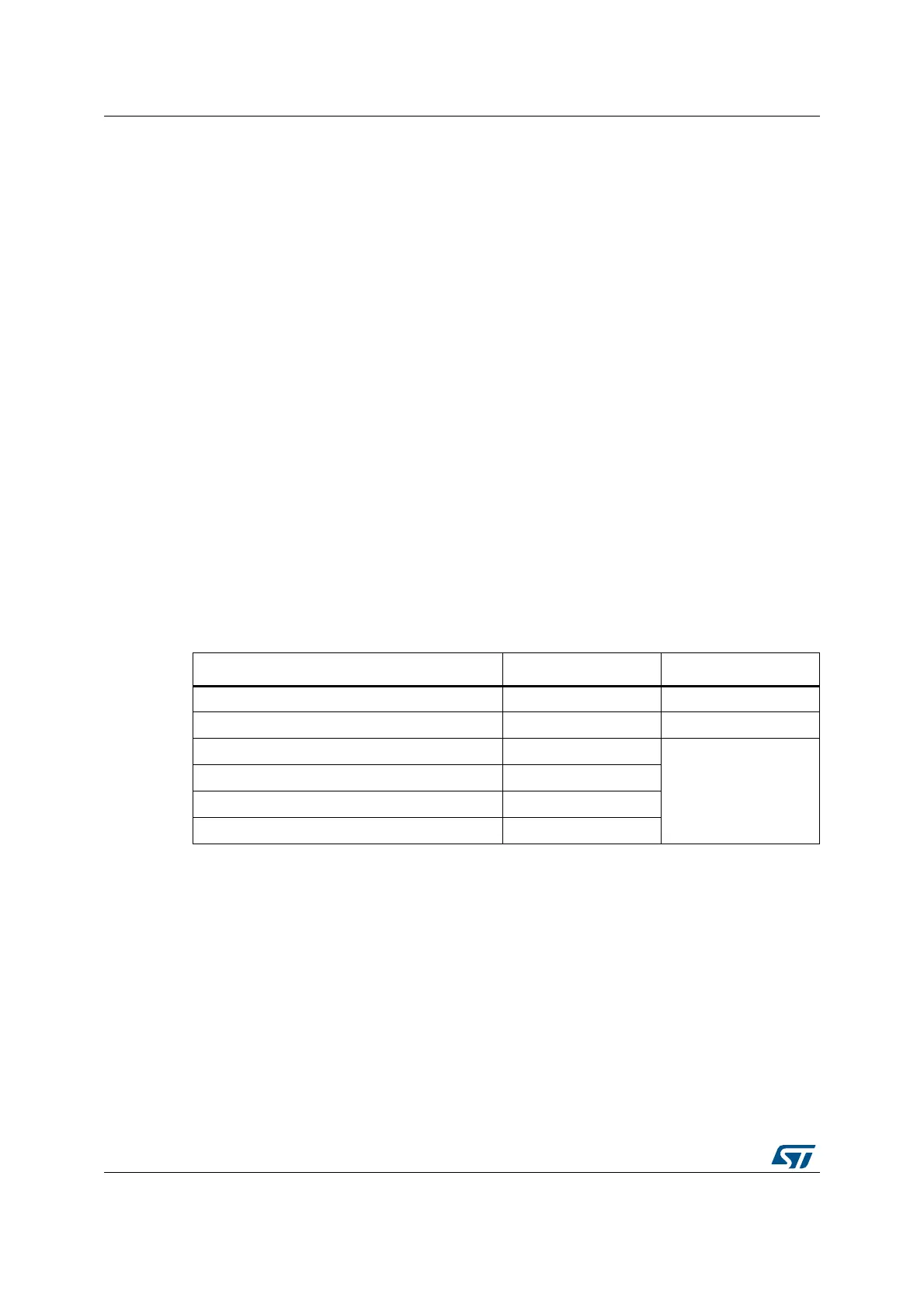

38.5 SPI interrupts

During SPI communication an interrupts can be generated by the following events:

• Transmit TXFIFO ready to be loaded

• Data received in Receive RXFIFO

• Master mode fault

• Overrun error

• TI frame format error

•

CRC protocol error

Interrupts can be enabled and disabled separately.

Table 206. SPI interrupt requests

Interrupt event Event flag Enable Control bit

Transmit TXFIFO ready to be loaded TXE TXEIE

Data received in RXFIFO RXNE RXNEIE

Master Mode fault event MODF

ERRIE

Overrun error OVR

TI frame format error FRE

CRC protocol error CRCERR

Loading...

Loading...