DocID024597 Rev 3 759/1693

RM0351 Advanced-control timers (TIM1/TIM8)

856

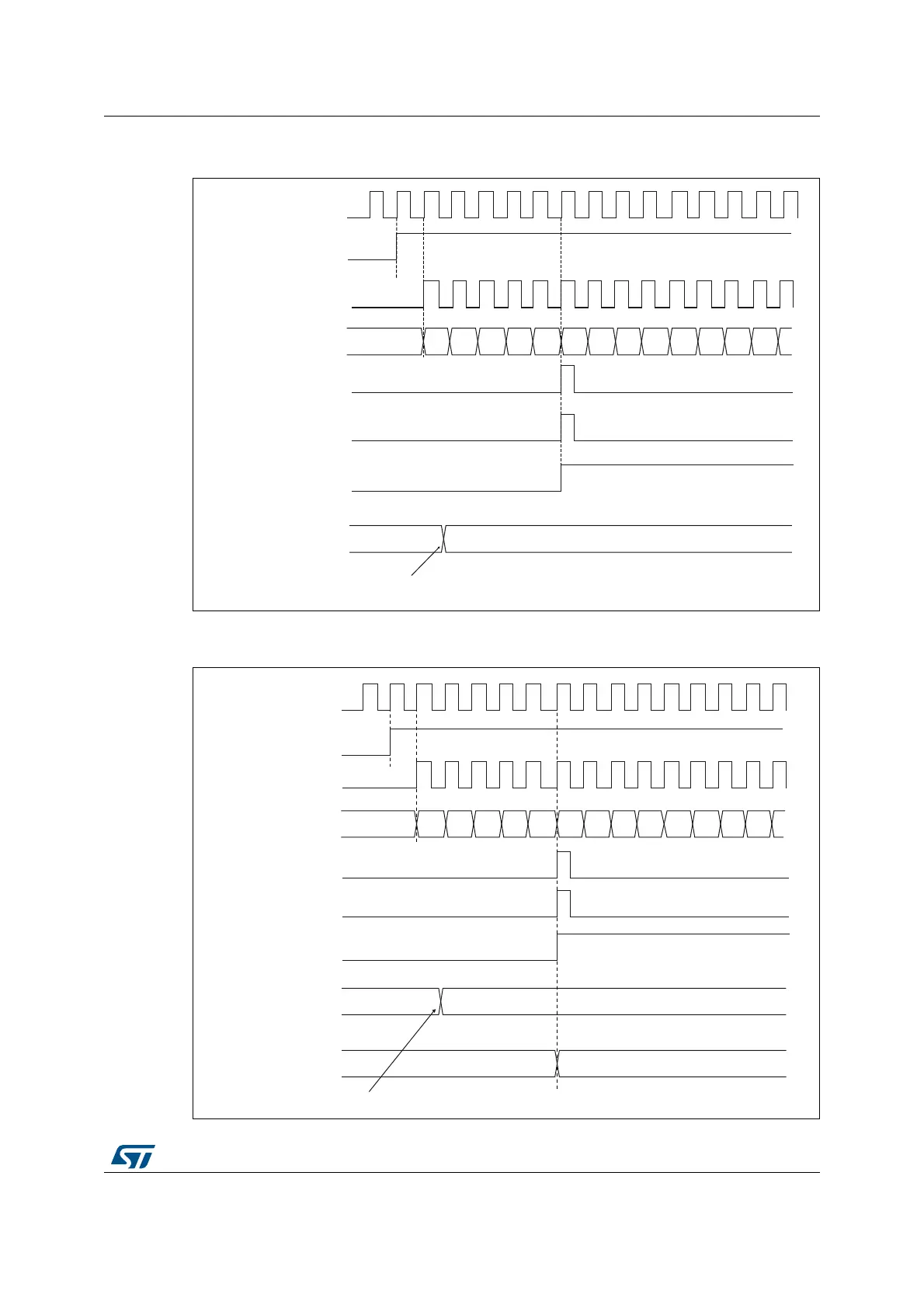

Figure 195. Counter timing diagram, update event when ARPE=0 (TIMx_ARR not

preloaded)

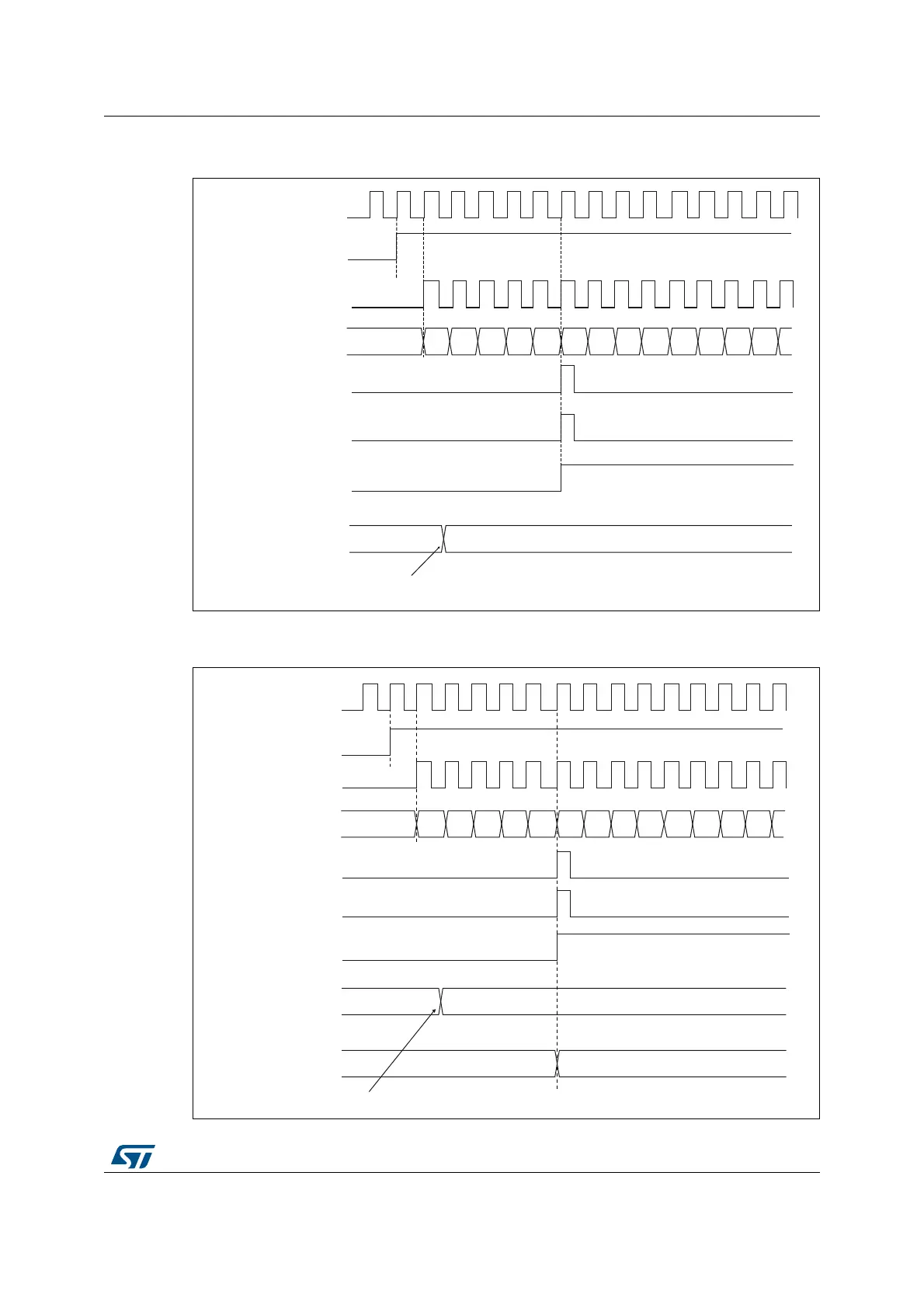

Figure 196. Counter timing diagram, update event when ARPE=1 (TIMx_ARR

preloaded)

&& ϯϲ

069

<ͺW^

dŝŵĞƌĐůŽĐŬс<ͺEd

ŽƵŶƚĞƌƌĞŐŝƐƚĞƌ

hƉĚĂƚĞĞǀĞŶƚ;hsͿ

ŽƵŶƚĞƌŽǀĞƌĨůŽǁ

hƉĚĂƚĞŝŶƚĞƌƌƵƉƚĨůĂŐ;h/&Ϳ

ϬϬ

ϬϮ

Ϭϯ Ϭϰ Ϭϱ

Ϭϲ

ϬϳϯϮ

ϯϯ

ϯϰ ϯϱ

ϯϲϯϭ

Ϭϭ

E

ƵƚŽͲƌĞůŽĂĚƉƌĞůŽĂĚƌĞŐŝƐƚĞƌ

tƌŝƚĞĂŶĞǁǀĂůƵĞŝŶd/DdžͺZZ

069

)

&.B36&

7LPHUFORFN &.B&17

&RXQWHUUHJLVWHU

8SGDWHHYHQW8(9

&RXQWHURYHUIORZ

8SGDWHLQWHUUXSWIODJ

8,)

)

)

) )

))

&(1

$XWRUHORDGSUHORDG

UHJLVWHU

:ULWHDQHZYDOXHLQ7,0[B$55

$XWRUHORDGVKDGRZ

UHJLVWHU

)

Loading...

Loading...