DocID024597 Rev 3 1517/1693

RM0351 USB on-the-go full-speed (OTG_FS)

1644

As the OTG_FS core is able to fill in the 1.25 Kbyte RAM buffer very efficiently, and as

1.25 Kbyte of transmit/receive data is more than enough to cover a full speed frame, the

USB system is able to withstand the maximum full-speed data rate for up to one USB frame

(1 ms) without any CPU intervention.

43.13 OTG_FS interrupts

When the OTG_FS controller is operating in one mode, either device or host, the application

must not access registers from the other mode. If an illegal access occurs, a mode

mismatch interrupt is generated and reflected in the Core interrupt register (MMIS bit in the

OTG_GINTSTS register). When the core switches from one mode to the other, the registers

in the new mode of operation must be reprogrammed as they would be after a power-on

reset.

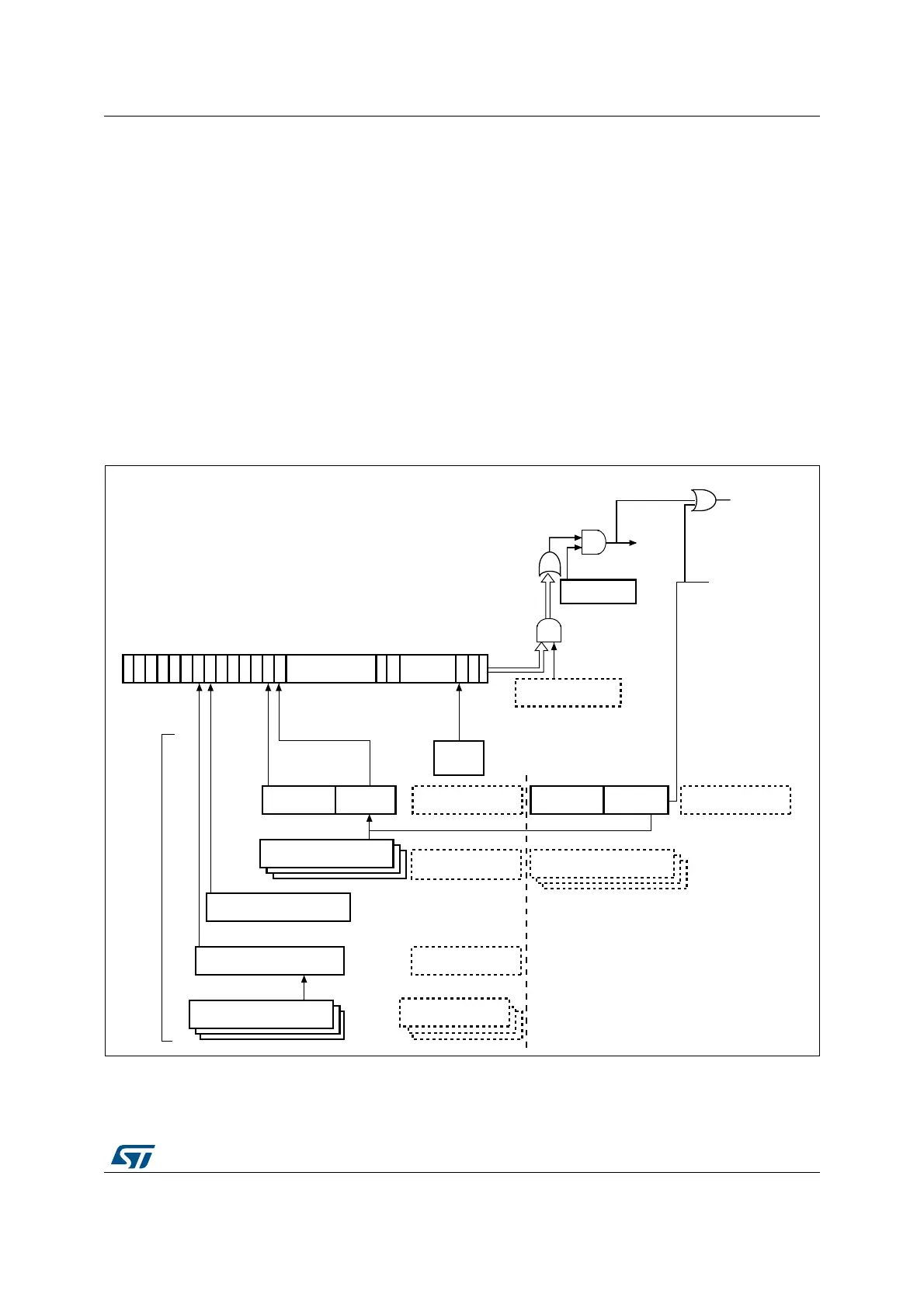

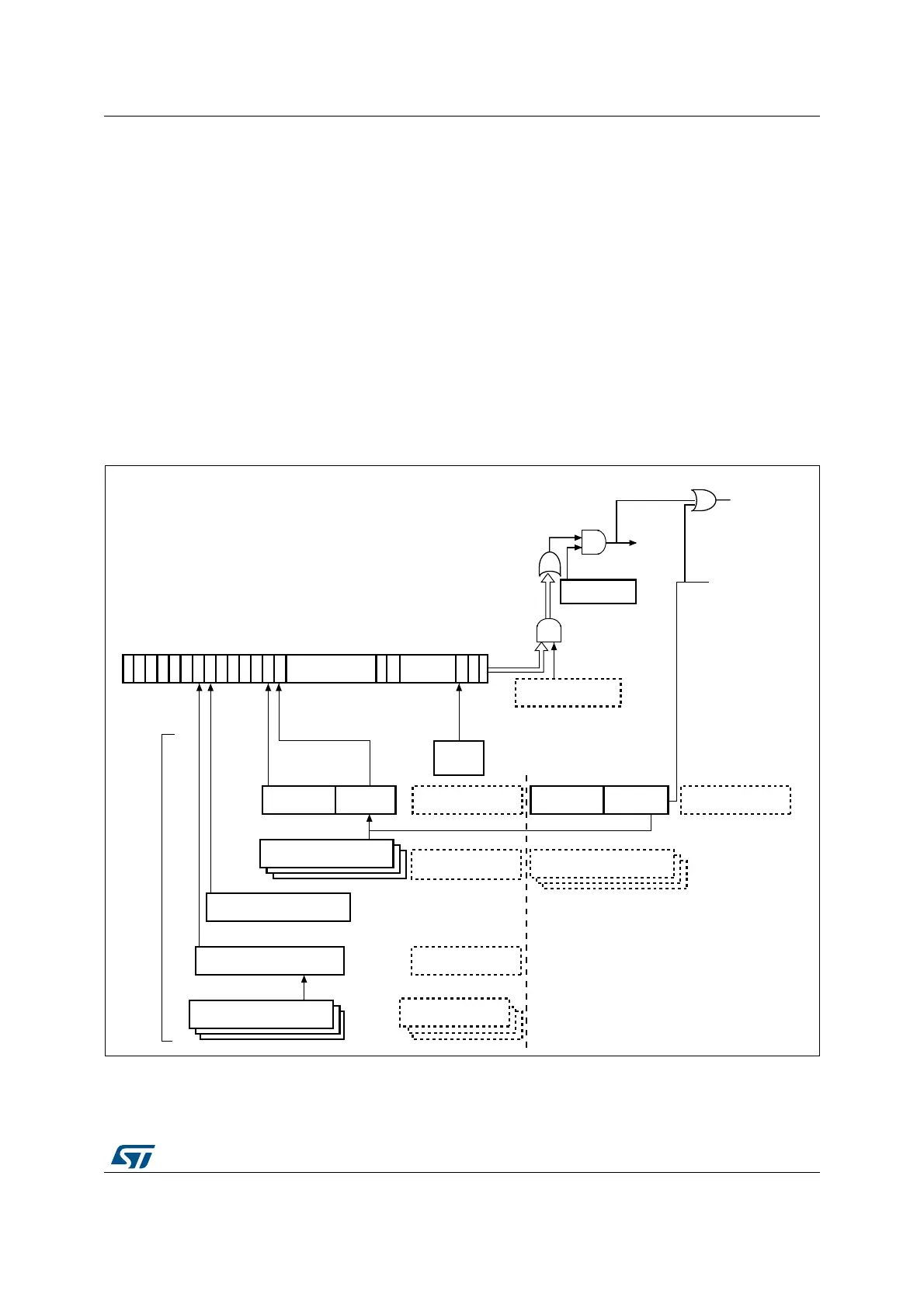

Figure 501 shows the interrupt hierarchy.

Figure 501. Interrupt hierarchy

1. The core interrupt register bits are shown in OTG core interrupt register (OTG_GINTSTS) on page 1530.

!.$

/2

)NTERRUPT

'LOBALINTERRUPT

MASK"IT

!("CONFIGURATION

REGISTER

#OREINTERRUPTMASK

REGISTER

/4'

INTERRUPT

REGISTER

#OREINTERRUPT

REGISTER

$EVICE)./54ENDPOINT

INTERRUPTREGISTERSTO

$EVICEALLENDPOINTS

INTERRUPTREGISTER

/54ENDPOINTS

).ENDPOINTS

)NTERRUPT

SOURCES

(OSTPORTCONTROLANDSTATUS

REGISTER

(OSTALLCHANNELSINTERRUPT

REGISTER

(OSTCHANNELSINTERRUPT

MASKREGISTERSTO

(OSTALLCHANNELS

INTERRUPTMASKREGISTER

(OSTCHANNELSINTERRUPT

REGISTERSTO

$EVICEALLENDPOINTS

INTERRUPTMASKREGISTER

$EVICE)./54

ENDPOINTSCOMMON

INTERRUPTMASKREGISTER

-3V6

/2

!.$

$EVICEEACH)./54ENDPOINT

INTERRUPTMASKREGISTER

$EVICEEACHENDPOINT

INTERRUPTREGISTER

%0/54

%0).

$EVICEEACHENDPOINT

INTERRUPTMASKREGISTER

ENDP?INTERRUPT;=

ENDP?MULTI?PROC?INTRPT

Loading...

Loading...