DocID024597 Rev 3 1391/1685

RM0351 Single Wire Protocol Master Interface (SWPMI)

1392

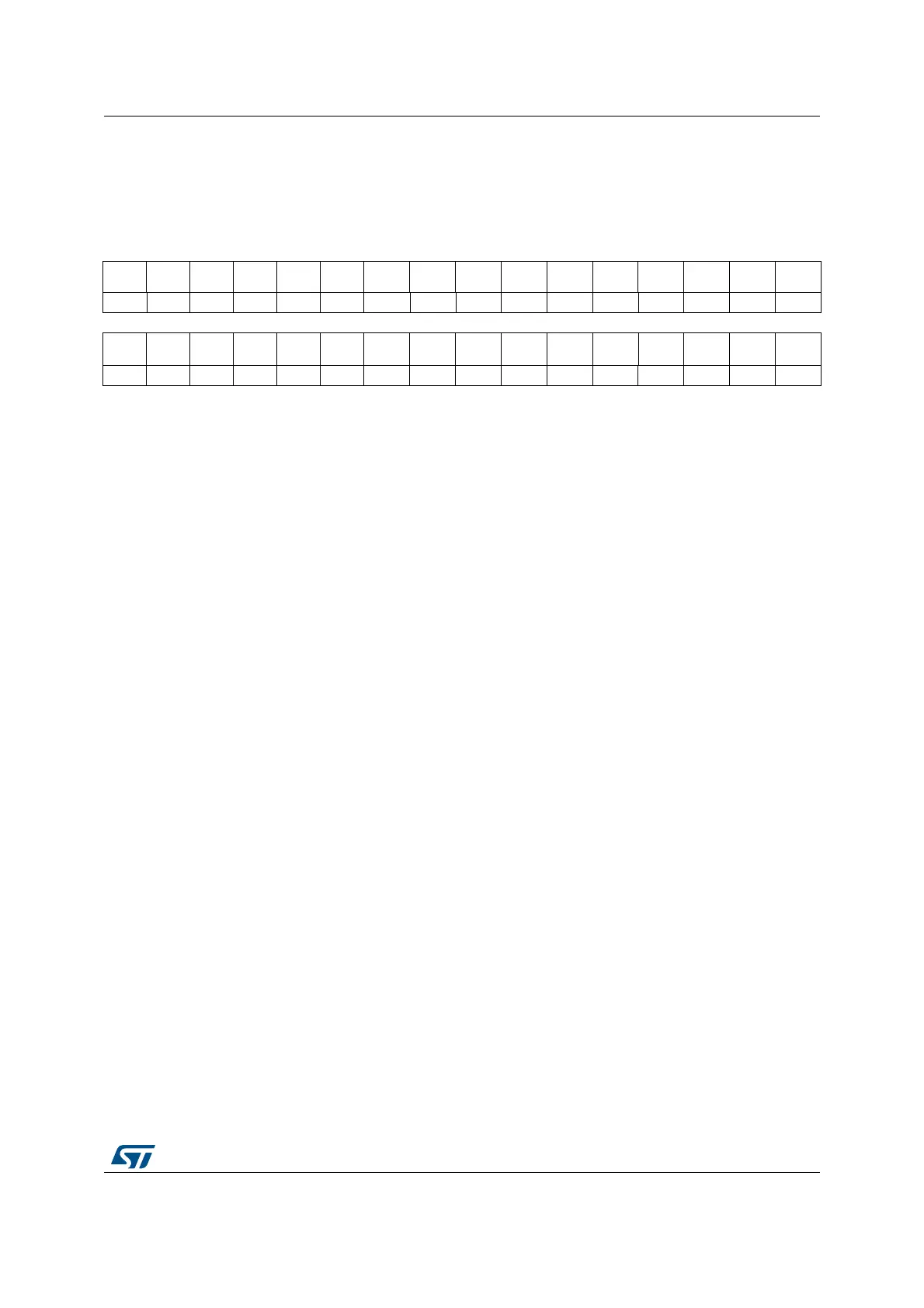

40.6.9 SWPMI Option register (SWPMI_OR)

Address offset: 0x24

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

SWP_

CLASS

SWP_

TBYP

rw rw

Bits 31:2 Reserved, must be kept at reset value

Bit 1 SWP_CLASS: SWP class selection

This bit is used to select the SWP class (refer to Section 40.3.2: SWP initialization and

activation).

0: Class C: SWPMI_IO uses directly VDD voltage to operate in class C.

This configuration must be selected when VDD is in the range [1.62 V to 1.98 V]

1: Class B: SWPMI_IO uses an internal voltage regulator to operate in class B.

This configuration must be selected when VDD is in the range [2.70 V to 3.30 V]

Bit 0 SWP_TBYP: SWP transceiver bypass

This bit is used to bypass the internal transceiver (SWPMI_IO), and connect an external

transceiver.

0: Internal transceiver is enabled. The external interface for SWPMI is SWPMI_IO

(SWPMI_RX, SWPMI_TX and SWPMI_SUSPEND signals are not available on GPIOs)

1: Internal transceiver is disabled. SWPMI_RX, SWPMI_TX and SWPMI_SUSPEND signals

are available as alternate function on GPIOs. This configuration is selected to connect an

external transceiver

Loading...

Loading...