Advanced encryption standard hardware accelerator (AES) RM0351

742/1693 DocID024597 Rev 3

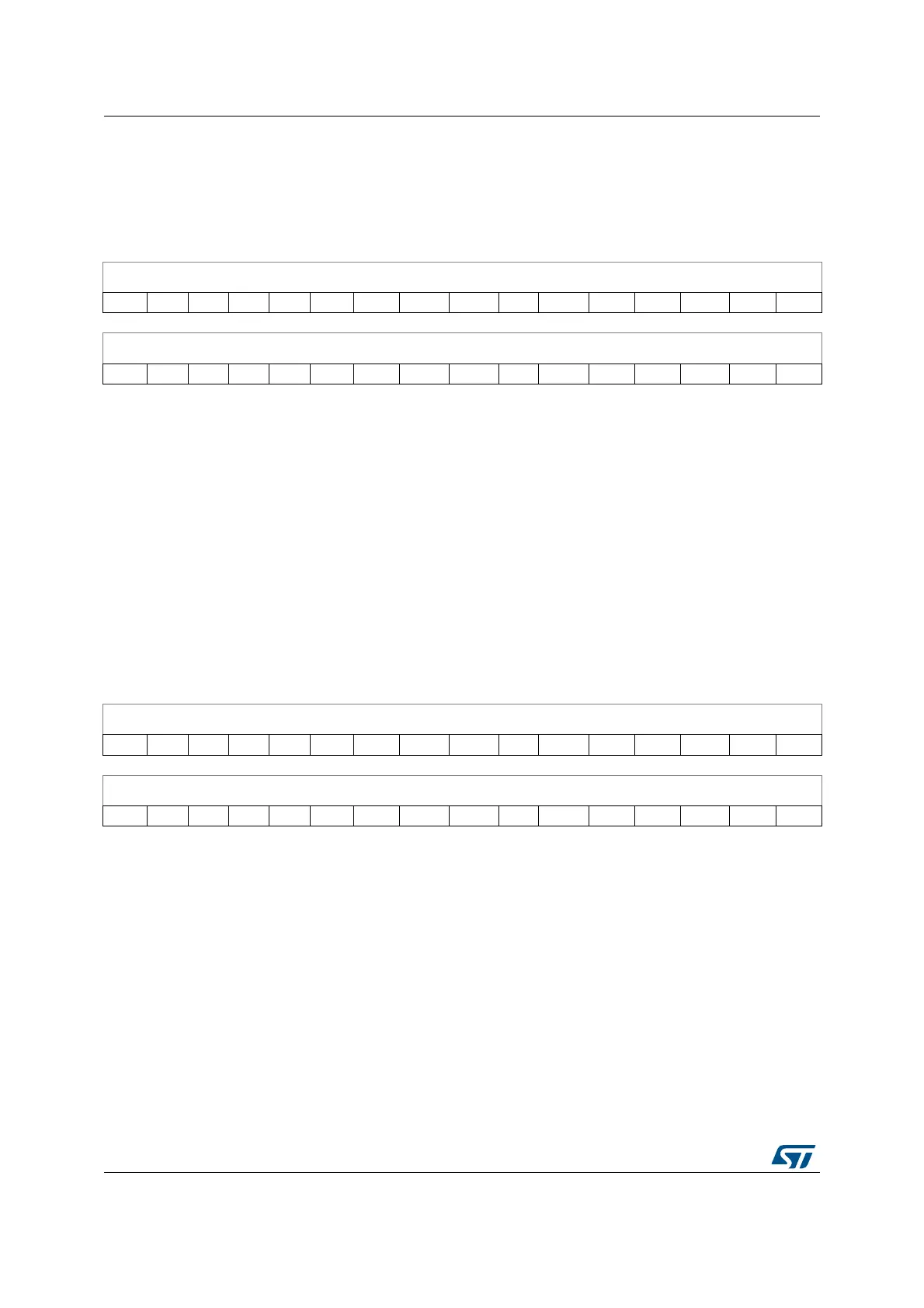

25.14.3 AES data input register (AES_DINR)

Address offset: 0x08

Reset value: 0x0000 0000

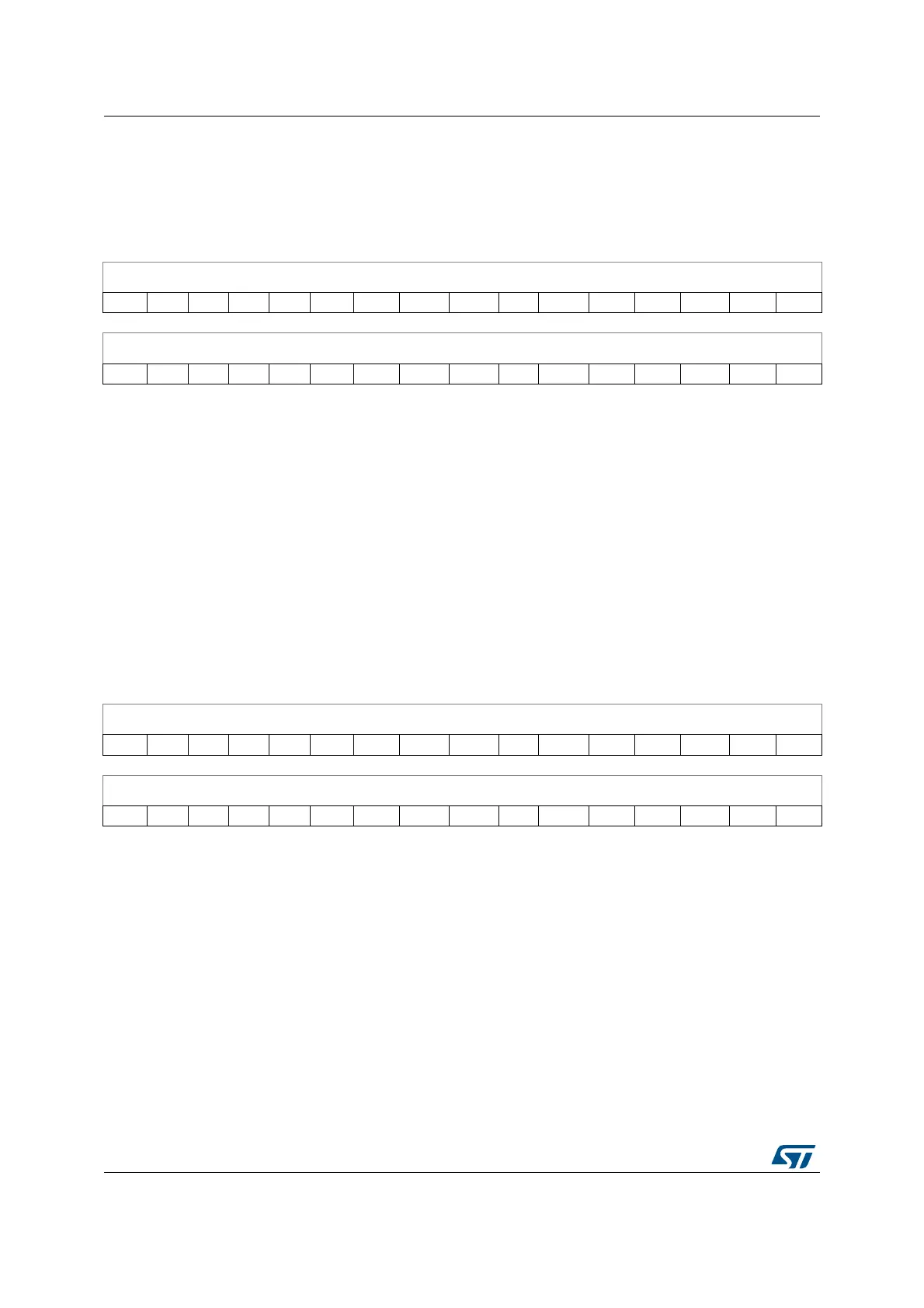

25.14.4 AES data output register (AES_DOUTR)

Address offset: 0x0C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DINR[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DINR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 DINR[31:0]: Data input register

This register must be written 4 times during the input phase:

– In mode 1 (encryption), 4 words must be written which represent the plain text from MSB to LSB.

– In mode 2 (key derivation), This register is not used because this mode concerns only derivative key

calculation starting from the AES_KEYRx register.

– In mode 3 (decryption) and 4 (Key derivation + decryption), 4 words must be written which represent

the cipher text MSB to LSB.

Note: This register must be accessed with 32-bit data width.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DOUTR[31:16]

r rrrr r r r r r r r r r r r

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DOUTR[15:0]

r rrrr r r r r r r r r r r r

Bits 31:0 DOUTR[31:0]: Data output register

This register is read only.

Once the CCF flag (computation complete flag) is set, reading this data register 4 times gives access

to the 128-bit output results:

– In mode 1 (encryption), the 4 words read represent the cipher text from MSB to LSB.

– In mode 2 (key derivation), there is no need to read this register because the derivative key is

located in the AES_KEYRx registers.

– In mode 3 (decryption) and mode 4 (key derivation + decryption), the 4 words read represent the

plain text from MSB to LSB.

Note: This register must be accessed with 32-bit data width.

Loading...

Loading...