Low-power universal asynchronous receiver transmitter (LPUART) RM0351

1266/1693 DocID024597 Rev 3

37.6 LPUART interrupts

The LPUART interrupt events are connected to the same interrupt vector (see Figure 407).

• During transmission: Transmission Complete, Clear to Send, Transmit data Register

empty or Framing error interrupt.

• During reception: Idle Line detection, Overrun error, Receive data register not empty,

Parity error, Noise Flag, Framing Error, Character match, etc.

These events generate an interrupt if the corresponding Enable Control Bit is set.

Stop 0, Stop 1 and Stop 2

The LPUART registers content is kept. The LPUART is able to wake up

the MCU from Stop 0, Stop 1 and Stop 2 modes when the UESM bit is set

and the LPUART clock is set to HSI16 or LSE.

The MCU wakeup from Stop 0, Stop 1 and 2 modes can be done using

either the standard RXNE or the WUF interrupt.

Standby

The LPUART is powered down and must be reinitialized when the device

has exited from Standby or Shutdown mode.

Shutdown

Table 202. Effect of low-power modes on the LPUART (continued)

Mode Description

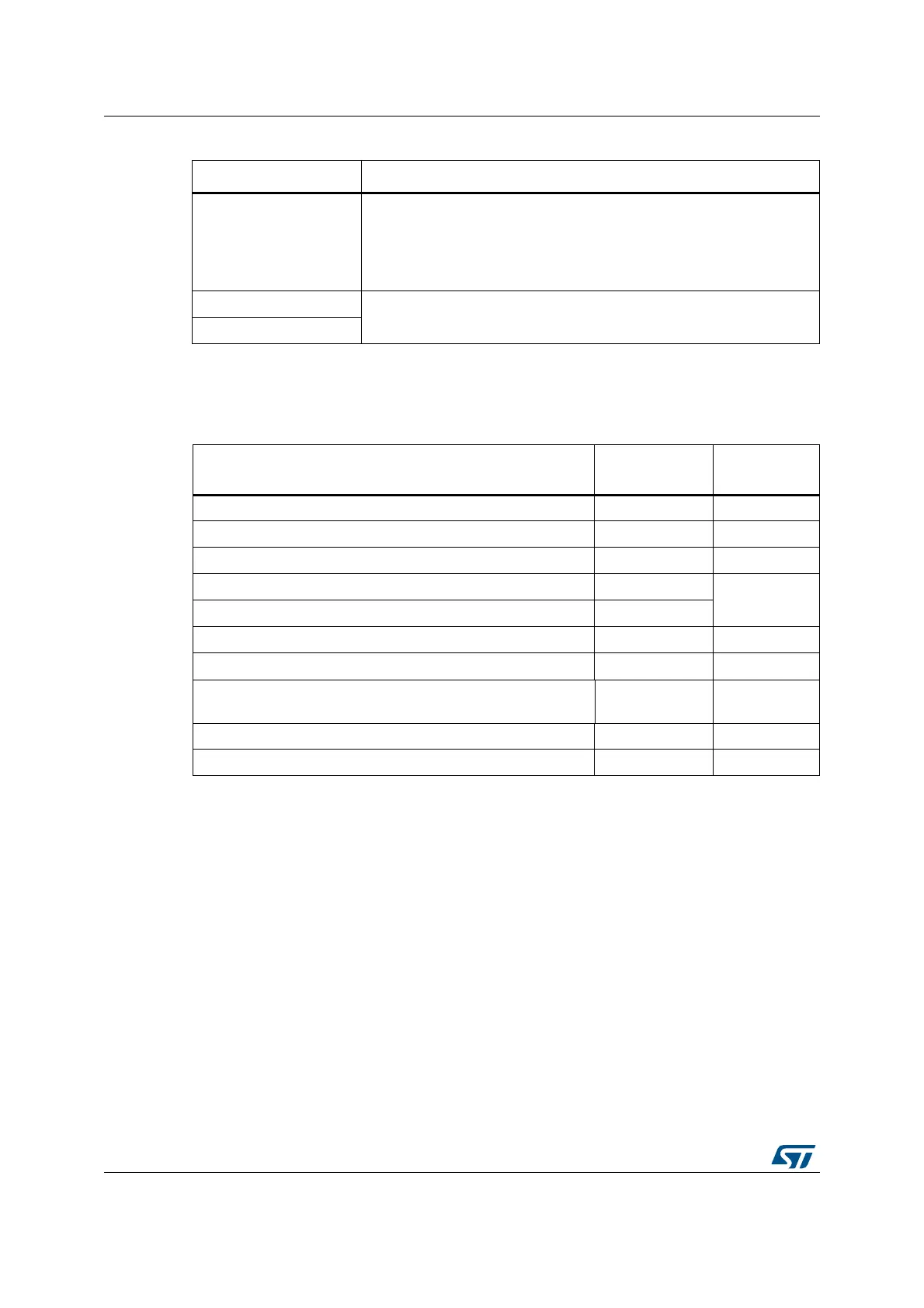

Table 203. LPUART interrupt requests

Interrupt event Event flag

Enable

Control bit

Transmit data register empty TXE TXEIE

CTS interrupt CTSIF CTSIE

Transmission Complete TC TCIE

Receive data register not empty (data ready to be read) RXNE

RXNEIE

Overrun error detected ORE

Idle line detected IDLE IDLEIE

Parity error PE PEIE

Noise Flag, Overrun error and Framing Error in multibuffer

communication.

NF or ORE or FE EIE

Character match CMF CMIE

Wakeup from Stop mode WUF

(1)

1. The wUF interrupt is active only in Stop mode.

WUFIE

Loading...

Loading...