DocID024597 Rev 3 1047/1693

RM0351 Independent watchdog (IWDG)

1055

32 Independent watchdog (IWDG)

32.1 Introduction

The devices feature an embedded watchdog peripheral which offers a combination of high

safety level, timing accuracy and flexibility of use. The Independent watchdog peripheral

serves to detect and resolve malfunctions due to software failure, and to trigger system

reset when the counter reaches a given timeout value.

The independent watchdog (IWDG) is clocked by its own dedicated low-speed clock (LSI)

and thus stays active even if the main clock fails.

The IWDG is best suited to applications which require the watchdog to run as a totally

independent process outside the main application, but have lower timing accuracy

constraints. For further information on the window watchdog, refer to Section 33 on page

1056.

32.2 IWDG main features

• Free-running downcounter

• Clocked from an independent RC oscillator (can operate in Standby and Stop modes)

• Conditional Reset

– Reset (if watchdog activated) when the downcounter value becomes less than

0x000

– Reset (if watchdog activated) if the downcounter is reloaded outside the window

32.3 IWDG functional description

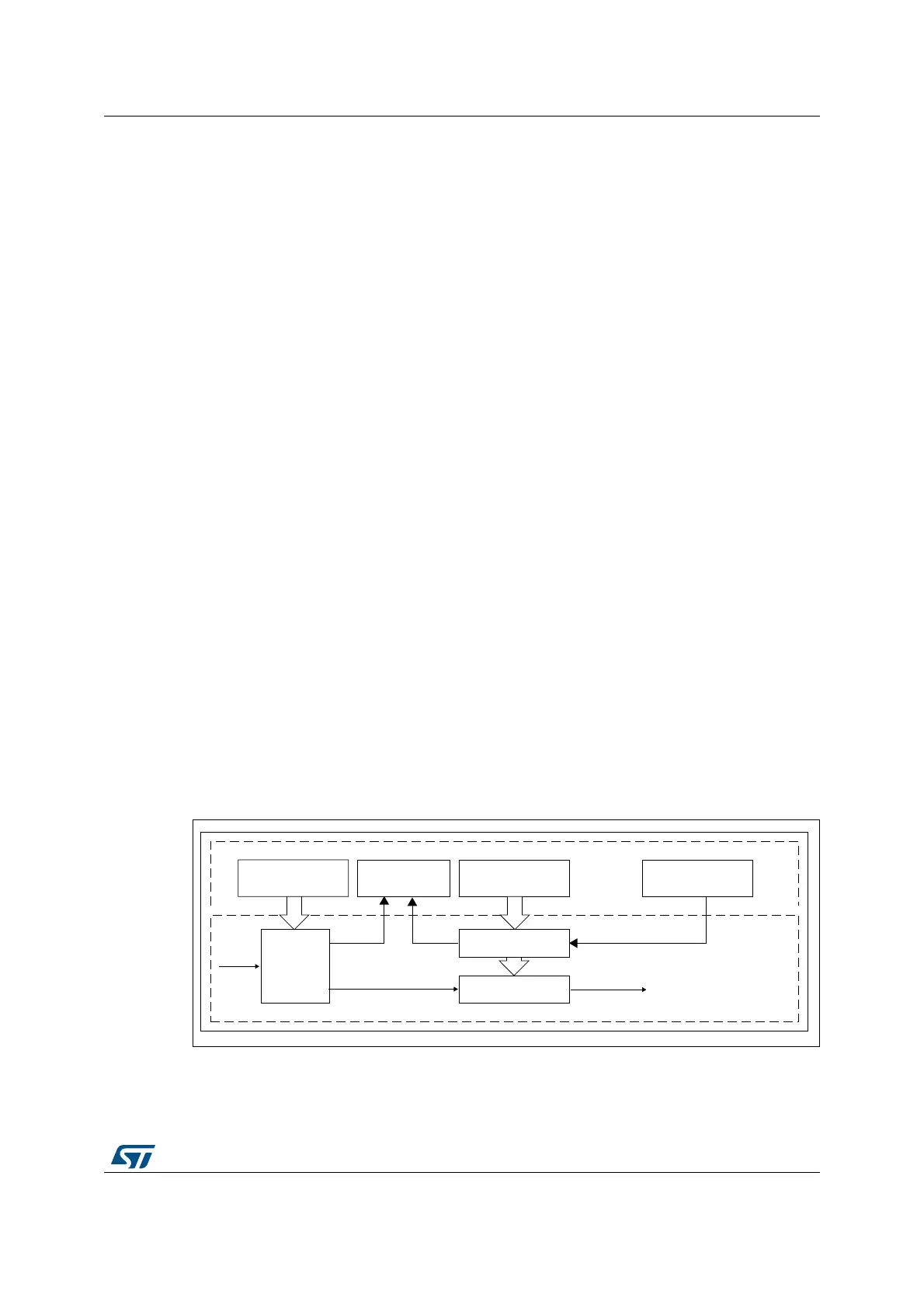

32.3.1 IWDG block diagram

Figure 348 shows the functional blocks of the independent watchdog module.

Figure 348. Independent watchdog block diagram

Note: The watchdog function is implemented in the V

CORE

voltage domain that is still functional in

Stop and Standby modes.

069

,:'*UHVHW

/6,

N+]

9

&25(

9

''

YROWDJHGRPDLQ

3UHVFDOHUUHJLVWHU

,:'*B35

6WDWXVUHJLVWHU

,:'*B65

5HORDGUHJLVWHU

,:'*B5/5

.H\UHJLVWHU

,:'*B.5

ELWUHORDGYDOXH

ELWGRZQFRXQWHU

ELW

SUHVFDOHU

Loading...

Loading...