DocID024597 Rev 3 1467/1693

RM0351 Controller area network (bxCAN)

1494

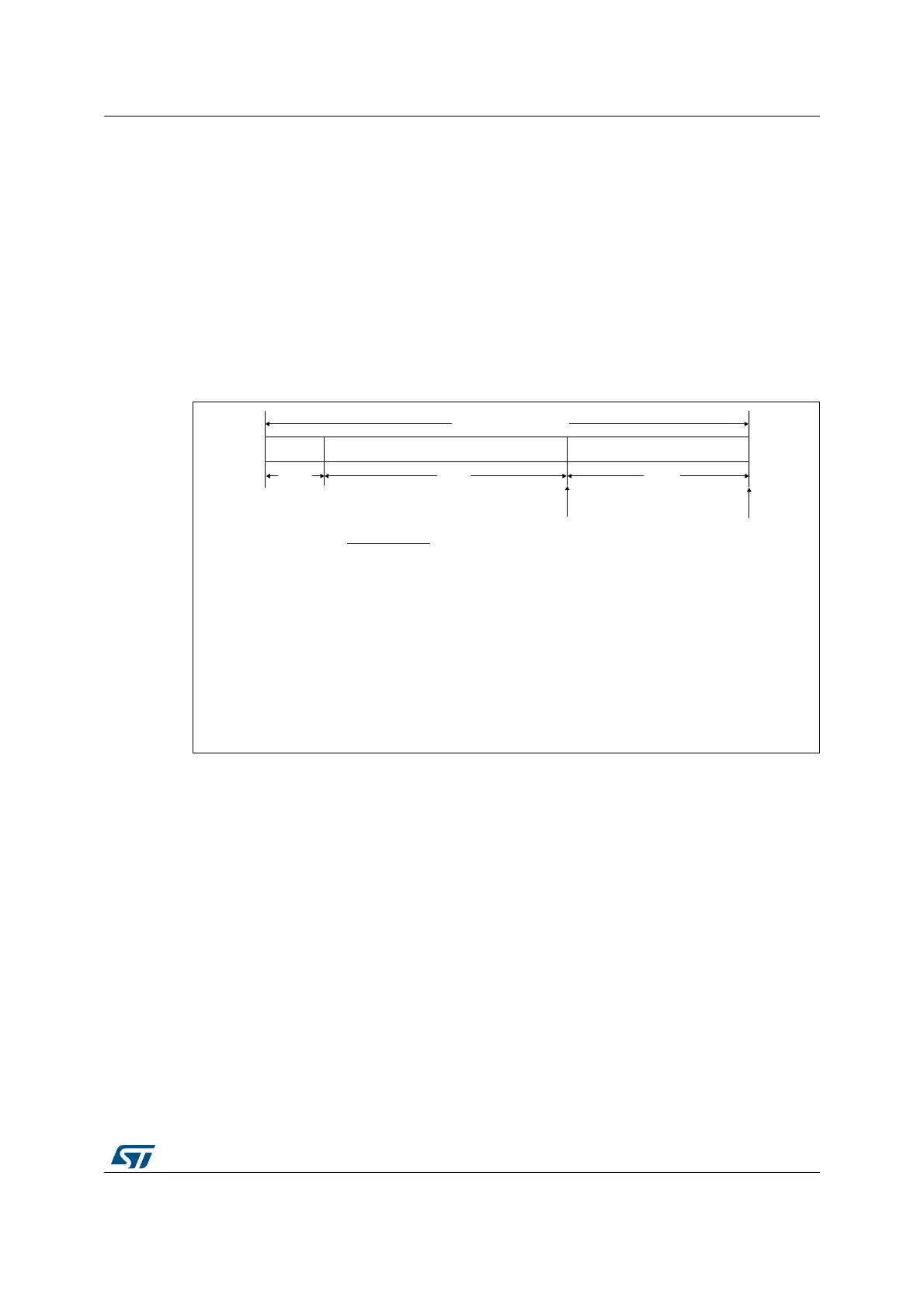

A valid edge is defined as the first transition in a bit time from dominant to recessive bus

level provided the controller itself does not send a recessive bit.

If a valid edge is detected in BS1 instead of SYNC_SEG, BS1 is extended by up to SJW so

that the sample point is delayed.

Conversely, if a valid edge is detected in BS2 instead of SYNC_SEG, BS2 is shortened by

up to SJW so that the transmit point is moved earlier.

As a safeguard against programming errors, the configuration of the Bit Timing Register

(CAN_BTR) is only possible while the device is in Standby mode.

Note: For a detailed description of the CAN bit timing and resynchronization mechanism, please

refer to the ISO 11898 standard.

Figure 489. Bit timing

6<1&B6(*

%,76(*0(17%6

120,1$/%,77,0(

[W

T

W

%6

6$03/(32,17 75$160,732,17

1RPLQDO%LW7LPH [WTW%6W%6

ZLWK

W

%6 WT[76>@

W

T %53>@[W3&/.

ZKHUHWTUHIHUVWRWKHWLPHTXDQWXP

W

3&/. WLPHSHULRGRIWKH$3%FORFN

%DXG5DWH

1RPLQDO%LW7LPH

069

%,76(*0(17%6

W%6

W%6 WT[76>@

%53>@76>@76>@DUHGHILQHGLQWKH&$1B%75UHJLVWHU

Loading...

Loading...