DocID024597 Rev 3 479/1693

RM0351 Analog-to-digital converters (ADC)

540

There are no changes for conversion timings in oversampled mode: the sample time is

maintained equal during the whole oversampling sequence. A new data is provided every N

conversions, with an equivalent delay equal to N x T

CONV

= N x (t

SMPL

+ t

SAR

). The flags are

set as follow:

• the end of the sampling phase (EOSMP) is set after each sampling phase

• the end of conversion (EOC) occurs once every N conversions, when the oversampled

result is available

• the end of sequence (EOS) occurs once the sequence of oversampled data is

completed (i.e. after N x sequence length conversions total)

Single ADC operating modes support when oversampling

In oversampling mode, most of the ADC operating modes are maintained:

• Single or continuous mode conversions

• ADC conversions start either by software or with triggers

• ADC stop during a conversion (abort)

• Data read via CPU or DMA with overrun detection

• Low-power modes (AUTDLY)

• Programmable resolution: in this case, the reduced conversion values (as per RES[1:0]

bits in ADCx_CFGR1 register) are accumulated, truncated, rounded and shifted in the

same way as 12-bit conversions are

Note: The alignment mode is not available when working with oversampled data. The ALIGN bit in

ADCx_CFGR1 is ignored and the data are always provided right-aligned.

Note: Offset correction is not supported in oversampling mode. When ROVSE and/or JOVSE bit is

set, the value of the OFFSETy_EN bit in ADCx_OFRy register is ignored (considered as

reset).

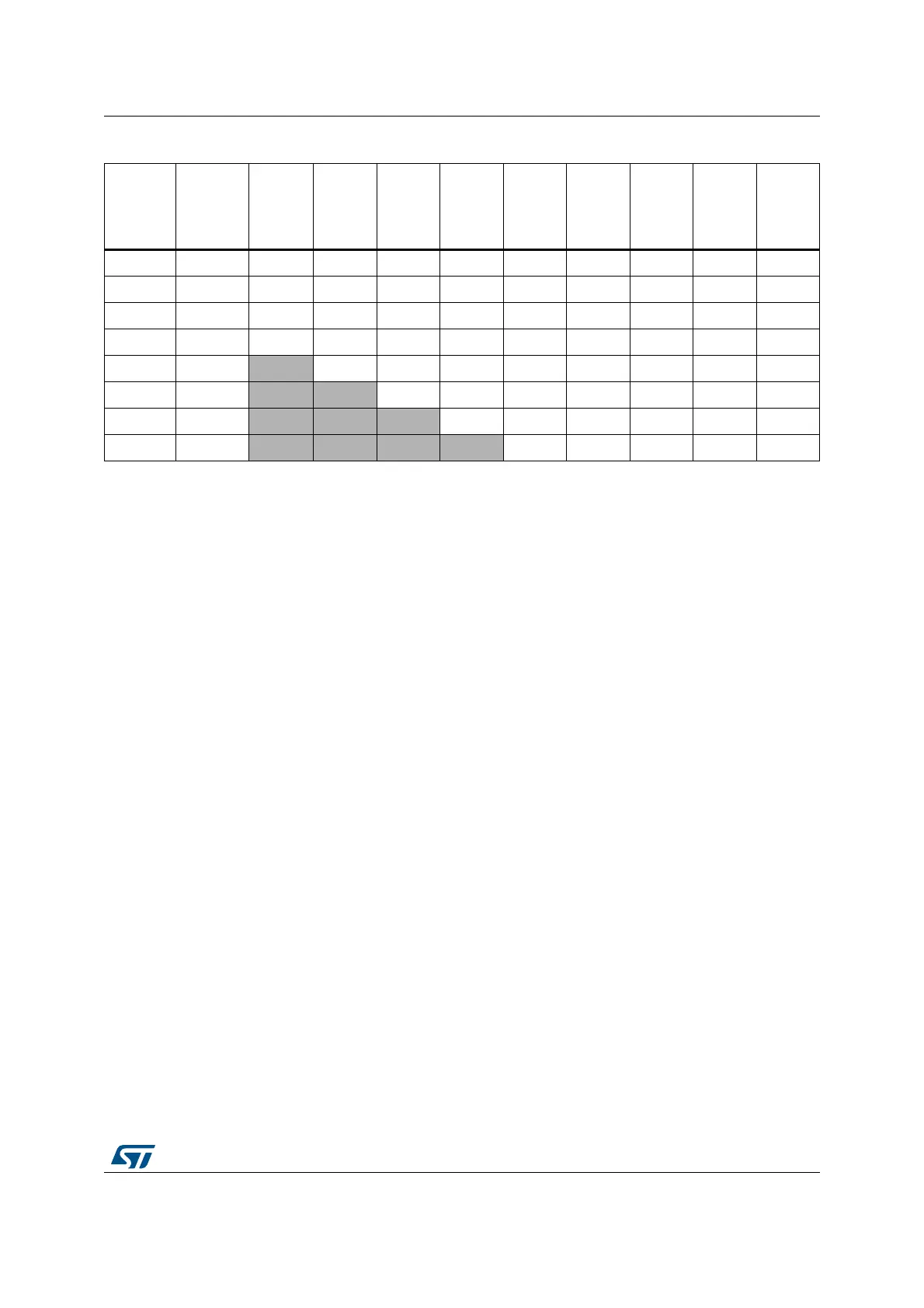

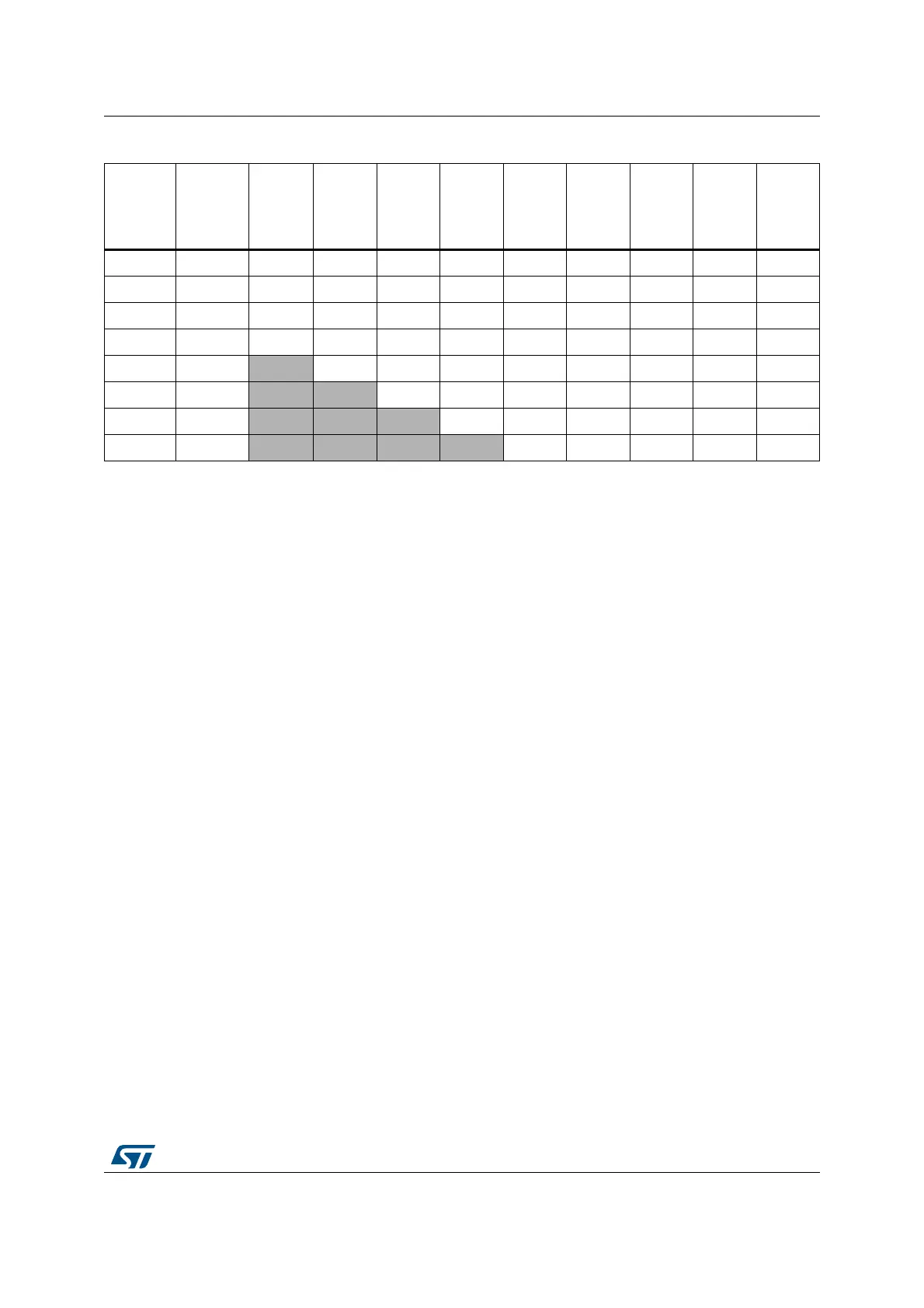

Table 95. Maximum output results versus N and M (gray cells indicate truncation)

Over

sampling

ratio

Max

Raw data

No-shift

OVSS =

0000

1-bit

shift

OVSS =

0001

2-bit

shift

OVSS =

0010

3-bit

shift

OVSS =

0011

4-bit

shift

OVSS =

0100

5-bit

shift

OVSS =

0101

6-bit

shift

OVSS =

0110

7-bit

shift

OVSS =

0111

8-bit

shift

OVSS =

1000

2x 0x1FFE 0x1FFE 0x0FFF 0x0800 0x0400 0x0200 0x0100 0x0080 0x0040 0x020

4x 0x3FFC 0x3FFC 0x1FFE 0x0FFF 0x0800 0x0400 0x0200 0x0100 0x0080 0x0040

8x 0x7FF8 0x7FF8 0x3FFC 0x1FFE 0x0FFF 0x0800 0x0400 0x0200 0x0100 0x0080

16x 0xFFF0 0xFFF0 0x7FF8 0x3FFC 0x1FFE 0x0FFF 0x0800 0x0400 0x0200 0x0100

32x 0x1FFE0

0xFFE0 0xFFF0 0x7FF8 0x3FFC 0x1FFE 0x0FFF 0x0800 0x0400 0x0200

64x 0x3FFC0

0xFFC0 0xFFE0 0xFFF0 0x7FF8 0x3FFC 0x1FFE 0x0FFF 0x0800 0x0400

128x 0x7FF80

0xFF80 0xFFC0 0xFFE0 0xFFF0 0x7FF8 0x3FFC 0x1FFE 0x0FFF 0x0800

256x 0xFFF00

0xFF00 0xFF80 0xFFC0 0xFFE0 0xFFF0 0x7FF8 0x3FFC 0x1FFE 0x0FFF

Loading...

Loading...