Universal synchronous asynchronous receiver transmitter (USART) RM0351

1196/1693 DocID024597 Rev 3

36.5.5 Tolerance of the USART receiver to clock deviation

The asynchronous receiver of the USART works correctly only if the total clock system

deviation is less than the tolerance of the USART receiver. The causes which contribute to

the total deviation are:

• DTRA: Deviation due to the transmitter error (which also includes the deviation of the

transmitter’s local oscillator)

• DQUANT: Error due to the baud rate quantization of the receiver

• DREC: Deviation of the receiver’s local oscillator

• DTCL: Deviation due to the transmission line (generally due to the transceivers which

can introduce an asymmetry between the low-to-high transition timing and the high-to-

low transition timing)

where

DWU is the error due to sampling point deviation when the wakeup from Stop mode is

used.

when M[1:0] = 01:

when M[1:0] = 00:

when M[1:0] = 10:

t

WUSTOP

is the wakeup time from Stop mode, which is specified in the product

datasheet.

The USART receiver can receive data correctly at up to the maximum tolerated deviation

specified in Table 194 and Table 194 depending on the following choices:

• 9-, 10- or 11-bit character length defined by the M bits in the USARTx_CR1 register

• Oversampling by 8 or 16 defined by the OVER8 bit in the USARTx_CR1 register

• Bits BRR[3:0] of USARTx_BRR register are equal to or different from 0000.

• Use of 1 bit or 3 bits to sample the data, depending on the value of the ONEBIT bit in

the USARTx_CR3 register.

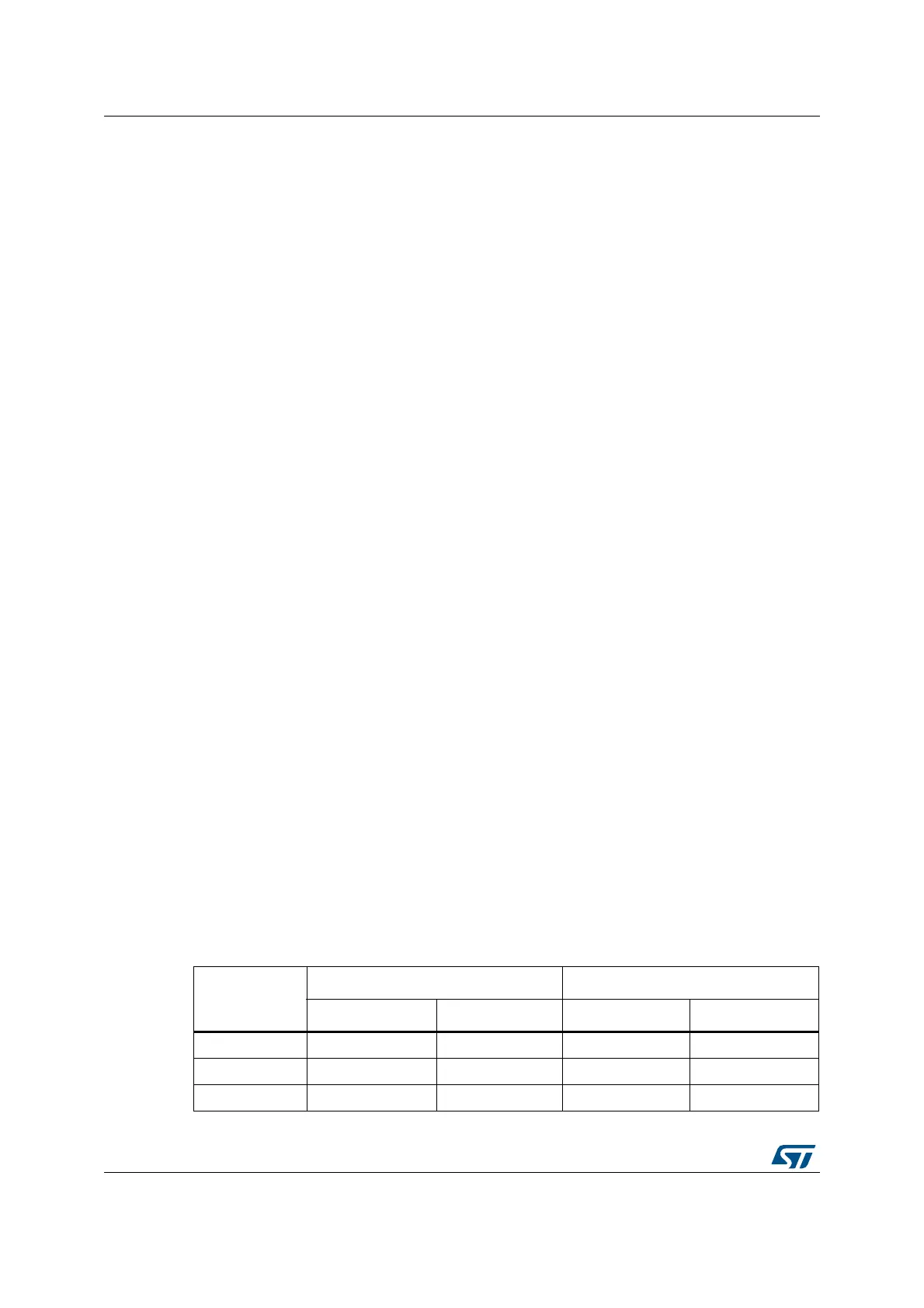

Table 194. Tolerance of the USART receiver when BRR [3:0] = 0000

M bits

OVER8 bit = 0 OVER8 bit = 1

ONEBIT=0 ONEBIT=1 ONEBIT=0 ONEBIT=1

00 3.75% 4.375% 2.50% 3.75%

01 3.41% 3.97% 2.27% 3.41%

10 4.16% 4.86% 2.77% 4.16%

DTRA DQUANT DREC DTCL DWU++++USART receiver′ s tolerance<

DWU

t

WUSTOP

11 Tbit×

-------------------------

=

DWU

t

WUSTOP

10 Tbit×

-------------------------

=

DWU

t

WUSTOP

9Tbit×

------------------------

=

Loading...

Loading...