Low-power timer (LPTIM) RM0351

1036/1693 DocID024597 Rev 3

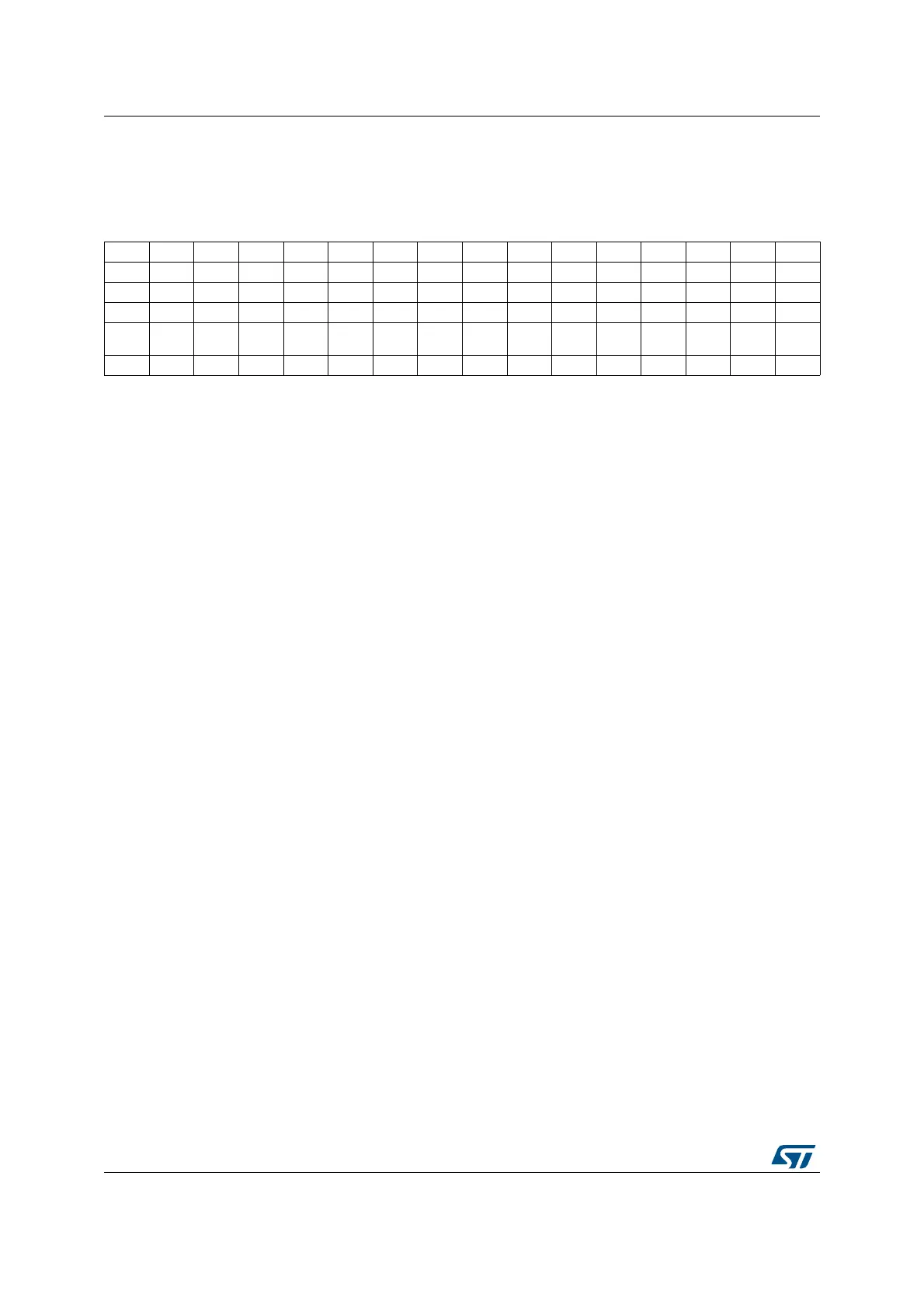

30.7.2 LPTIM interrupt clear register (LPTIMx_ICR)

Address offset: 0x04

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res.

DOWN

CF

UPCF

ARRO

KCF

CMPO

KCF

EXTTR

IGCF

ARRM

CF

CMPM

CF

wwwwwww

Bits 31:7 Reserved, must be kept at reset value.

Bit 6 DOWNCF: Direction change to down Clear Flag

Writing 1 to this bit clear the DOWN flag in the LPT_ISR register

Bit 5 UPCF: Direction change to UP Clear Flag

Writing 1 to this bit clear the UP flag in the LPT_ISR register

Bit 4 ARROKCF: Autoreload register update OK Clear Flag

Writing 1 to this bit clears the ARROK flag in the LPT_ISR register

Bit 3 CMPOKCF: Compare register update OK Clear Flag

Writing 1 to this bit clears the CMPOK flag in the LPT_ISR register

Bit 2 EXTTRIGCF: External trigger valid edge Clear Flag

Writing 1 to this bit clears the EXTTRIG flag in the LPT_ISR register

Bit 1 ARRMCF: Autoreload match Clear Flag

Writing 1 to this bit clears the ARRM flag in the LPT_ISR register

Bit 0 CMPMCF: compare match Clear Flag

Writing 1 to this bit clears the CMP flag in the LPT_ISR register

Loading...

Loading...