USB on-the-go full-speed (OTG_FS) RM0351

1564/1693 DocID024597 Rev 3

43.15.33 OTG device control register (OTG_DCTL)

Address offset: 0x804

Reset value: 0x0000 0002

Bits 1:0 DSPD: Device speed

Indicates the speed at which the application requires the core to enumerate, or the

maximum speed the application can support. However, the actual bus speed is determined

only after the chirp sequence is completed, and is based on the speed of the USB host to

which the core is connected.

00: Reserved

01: Reserved

10: Reserved

11: Full speed (USB 1.1 transceiver clock is 48 MHz)

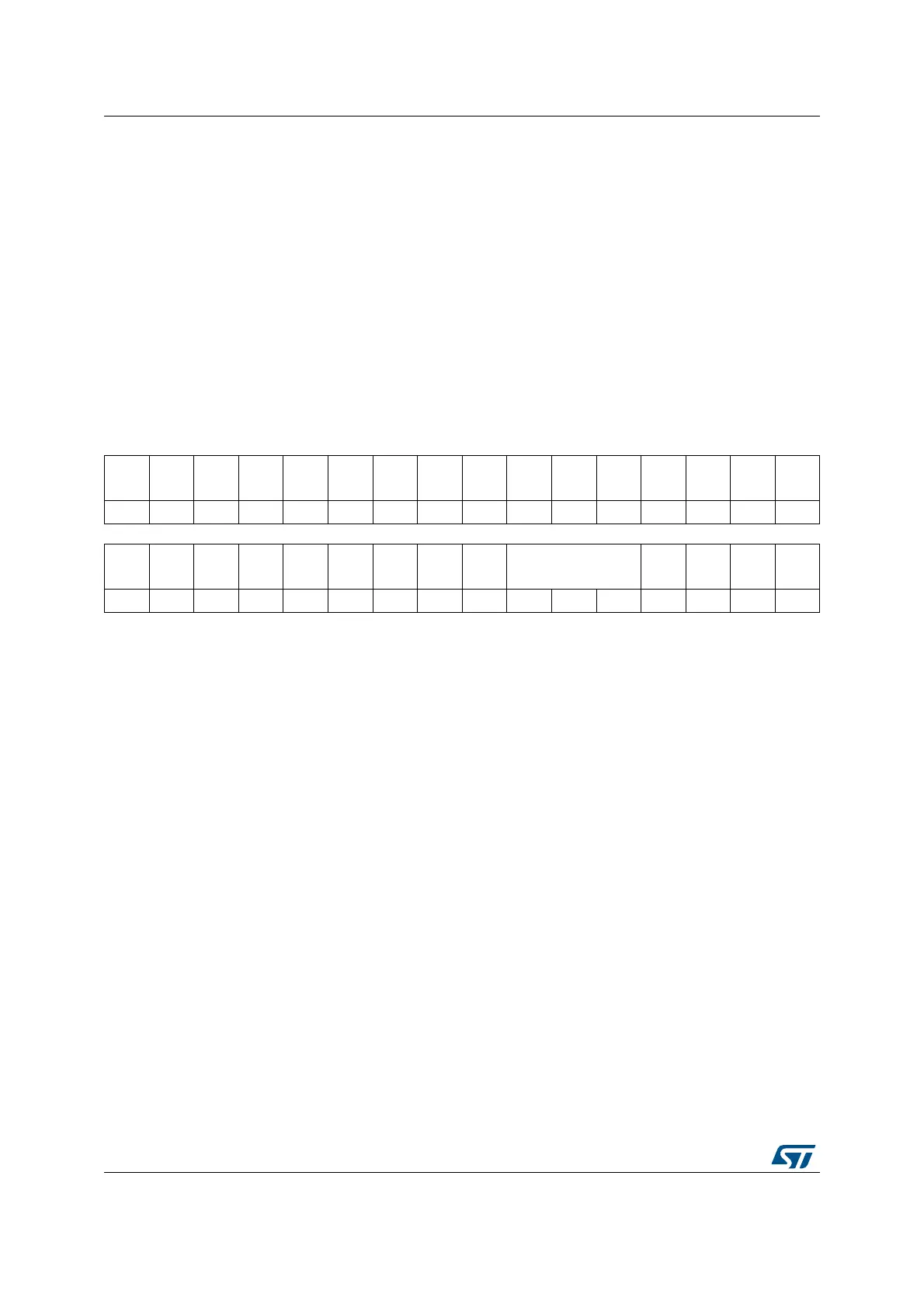

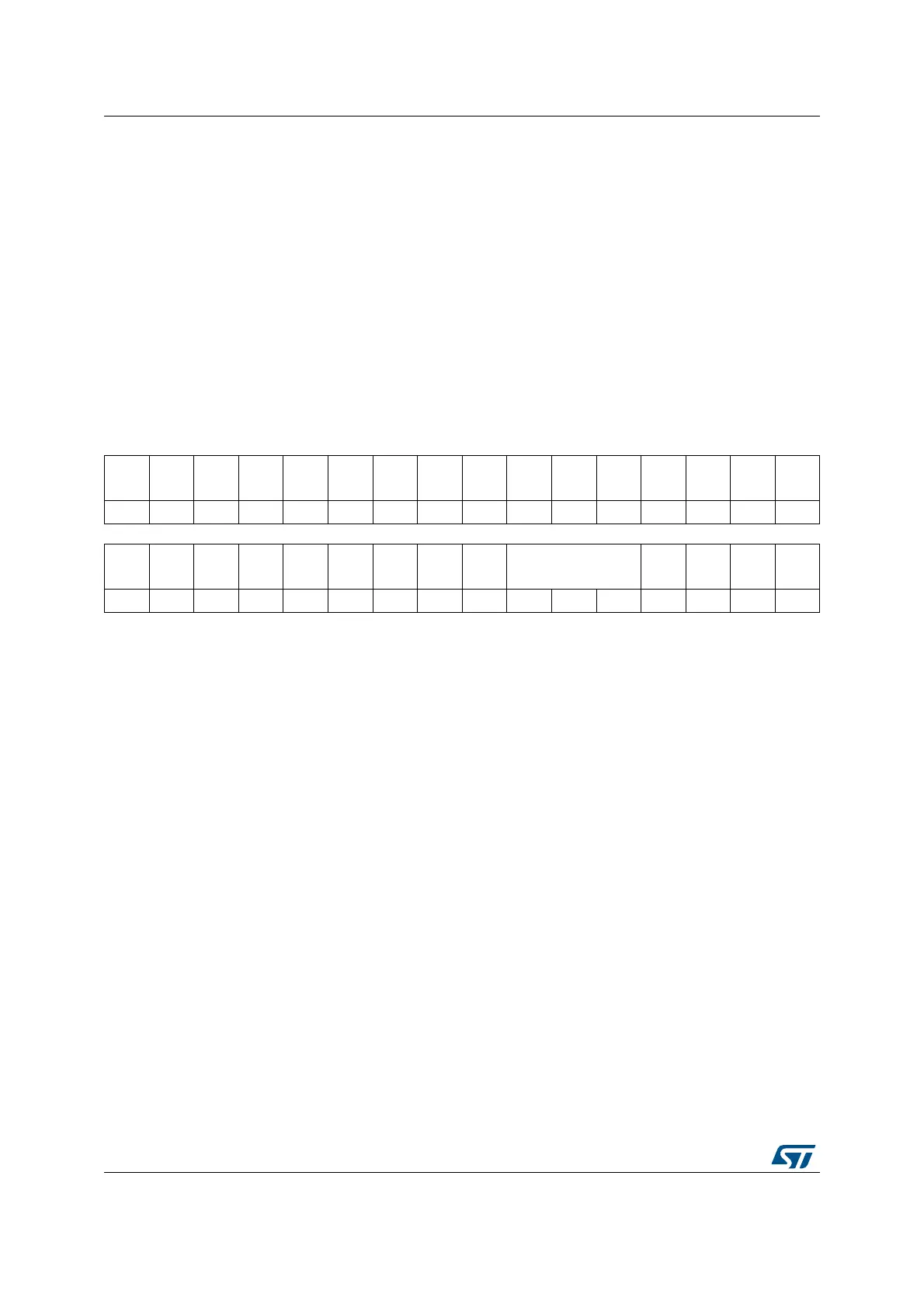

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

DS

BESL

RJCT

Res. Res.

rw

1514131211109876543210

Res. Res. Res. Res.

PO

PRG

DNE

CGO

NAK

SGO

NAK

CGI

NAK

SGI

NAK

TCTL

GON

STS

GIN

STS

SDIS

RWU

SIG

rwwwwwrwrwrwr rrwrw

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 DSBESLRJCT: Deep sleep BESL reject

Core rejects LPM request with BESL value greater than BESL threshold programmed.

NYET response is sent for LPM tokens with BESL value greater than BESL threshold. By

default, the deep sleep BESL reject feature is disabled.

Bits 17:12 Reserved, must be kept at reset value.

Bit 11 POPRGDNE: Power-on programming done

The application uses this bit to indicate that register programming is completed after a

wakeup from power down mode.

Bit 10 CGONAK: Clear global OUT NAK

A write to this field clears the Global OUT NAK.

Bit 9 SGONAK: Set global OUT NAK

A write to this field sets the Global OUT NAK.

The application uses this bit to send a NAK handshake on all OUT endpoints.

The application must set the this bit only after making sure that the Global OUT NAK

effective bit in the Core interrupt register (GONAKEFF bit in OTG_GINTSTS) is cleared.

Bit 8 CGINAK: Clear global IN NAK

A write to this field clears the Global IN NAK.

Bit 7 SGINAK: Set global IN NAK

A write to this field sets the Global non-periodic IN NAK.The application uses this bit to send

a NAK handshake on all non-periodic IN endpoints.

The application must set this bit only after making sure that the Global IN NAK effective bit

in the Core interrupt register (GINAKEFF bit in OTG_GINTSTS) is cleared.

Loading...

Loading...