Digital filter for sigma delta modulators (DFSDM) RM0351

606/1693 DocID024597 Rev 3

Note: This example shows 4 DFSDM interfaces and 8 input channels (max. configuration).

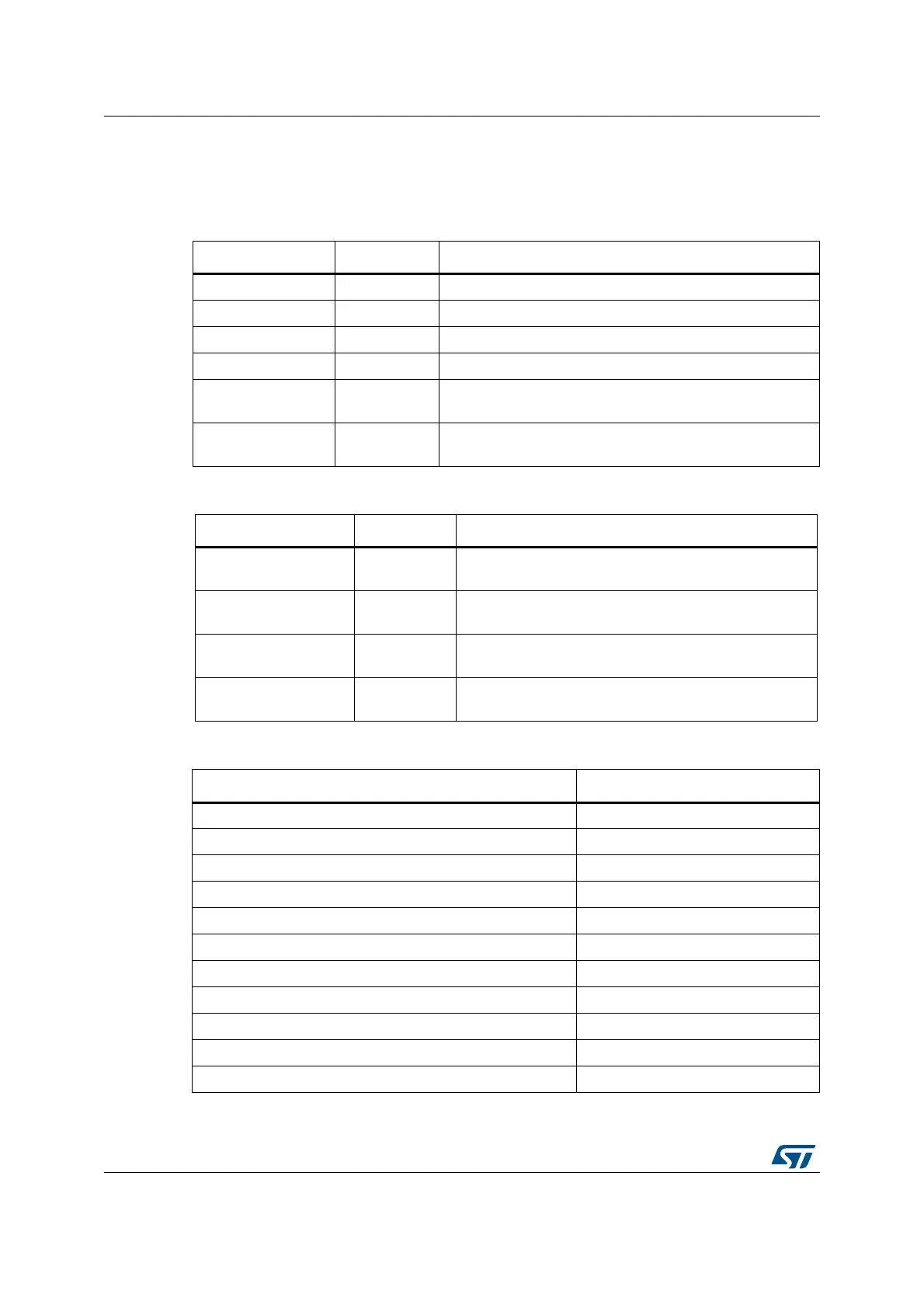

21.3.2 DFSDM pins and internal signals

Table 120. DFSDM external pins

Name Signal Type Remarks

VDD Power supply Digital power supply 1.65 - 3.6V.

VSS Power supply Digital ground power supply.

DFSDM_CKIN[7:0] Clock input Clock signal provided from external modulator. FT input.

DFSDM_DATIN[7:0] Data input Data signal provided from external modulator. FT input.

DFSDM_CKOUT Clock output

Clock output to provide clock signal into external

modulator.

DFSDM_EXTRG[1:0]

External trigger

signal

Input trigger from two EXTI signals to start analog

conversion (from GPIOs: EXTI11, EXTI15).

Table 121. DFSDM internal signals

Name Signal Type Remarks

DFSDM_INTRG[8:0]

Internal trigger

signal

Input trigger from internal trigger sources to start analog

conversion, see Table 122 for details.

DFSDM_BREAK[3:0]

break signal

output

Break signals event generation from Analog watchdog or

short-circuit detector

DFSDM_DMAREQ[3:0]

DMA request

signal

DMA request signal from each DFSDMx (x=0..3): end of

injected conversion event.

DFSDM_INT[3:0]

Interrupt

request signal

Interrupt signal for each DFSDMx (x=0..3)

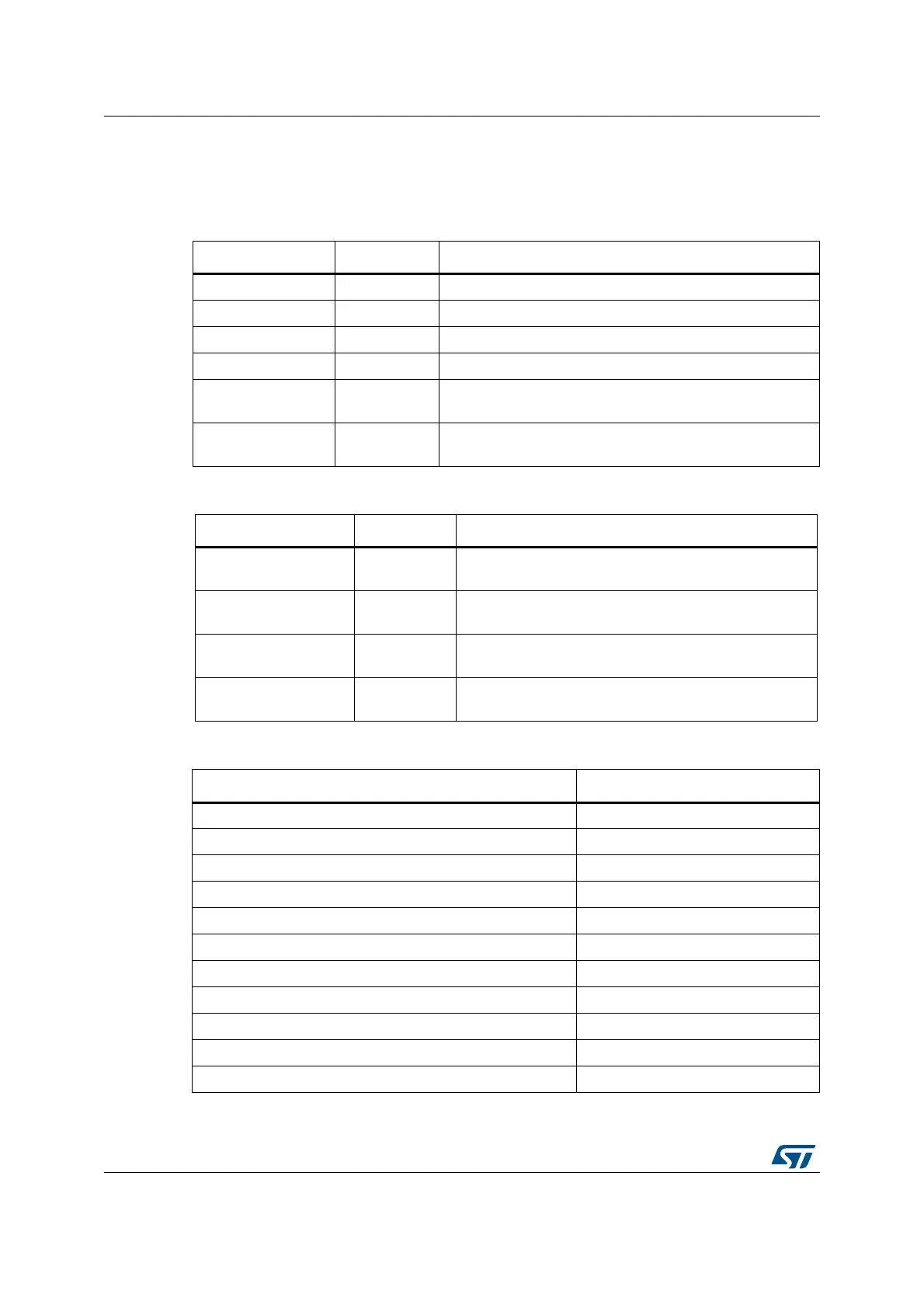

Table 122. DFSDM triggers connection

Trigger name Trigger source

DFSDM_INTRG[0] TIM1_TRGO

DFSDM_INTRG[1] TIM1_TRGO2

DFSDM_INTRG[2] TIM8_TRGO

DFSDM_INTRG[3] TIM8_TRGO2

DFSDM_INTRG[4] TIM3_TRGO

DFSDM_INTRG[5] TIM4_TRGO

DFSDM_INTRG[6] TIM16_OC1

DFSDM_INTRG[7] TIM6_TRGO

DFSDM_INTRG[8] TIM7_TRGO

DFSDM_EXTRG[0] EXTI11

DFSDM_EXTRG[1] EXTI15

Loading...

Loading...